STC8A8K64D4 Series Manual

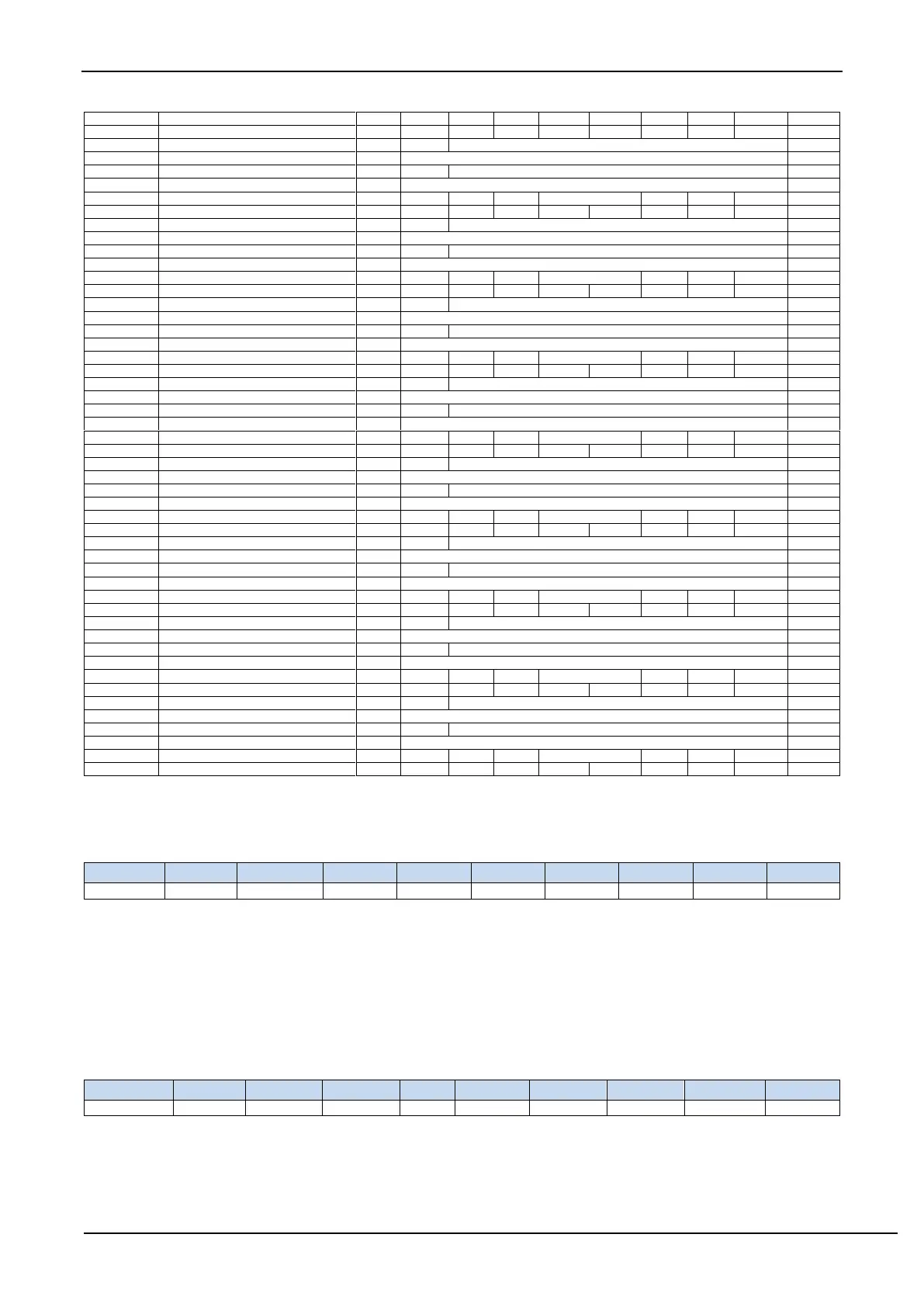

PWM Interrupt Flag Register

PWM Fault Detection Control Register

PWM0 Level Holding Control Register

PWM1 Level Holding Control Register

PWM2 Level Holding Control Register

PWM3 Level Holding Control Register

PWM4 Level Holding Control Register

PWM5 Level Holding Control Register

PWM6 Level Holding Control Register

PWM7 Level Holding Control Register

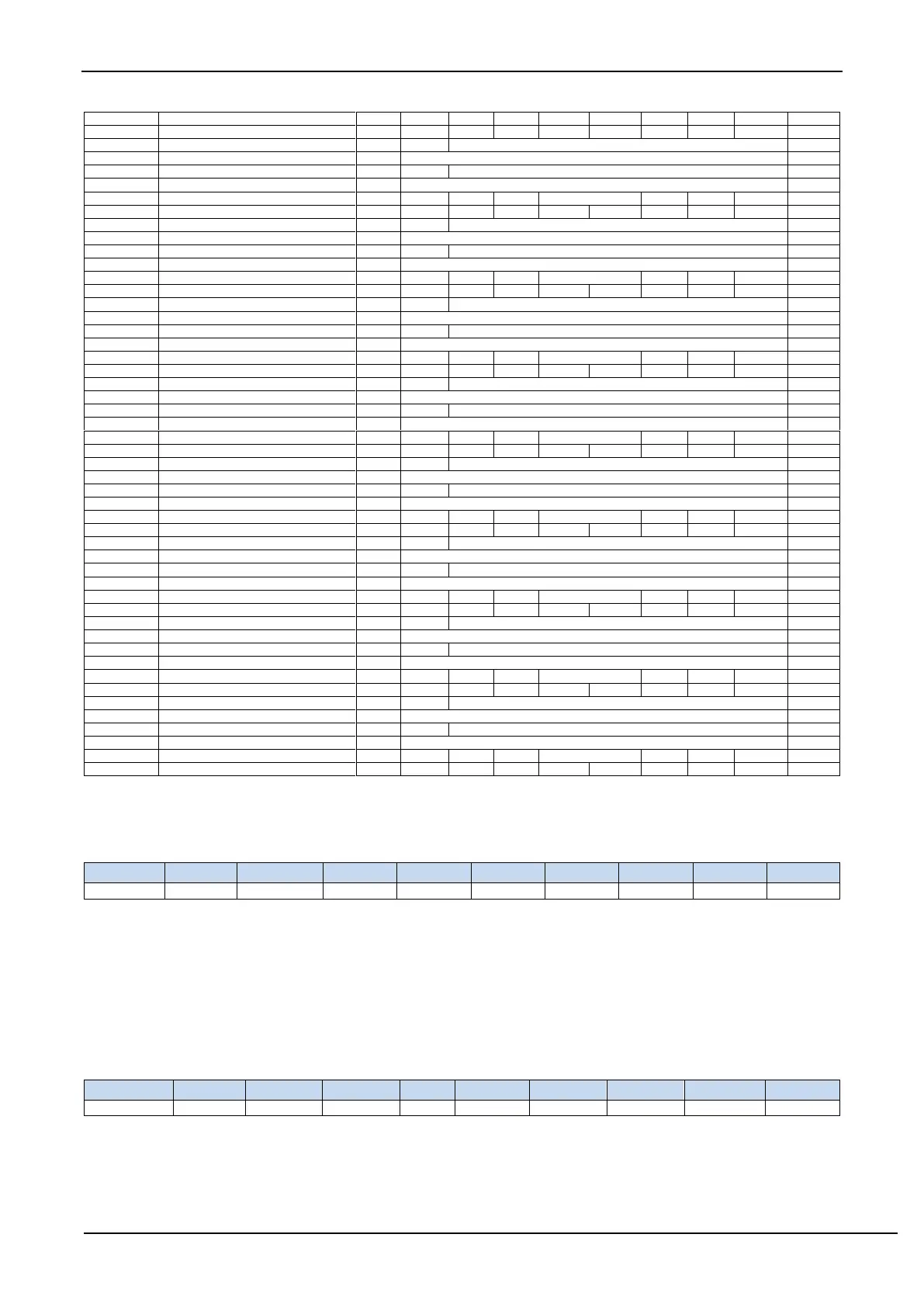

19.2.1 Enhanced PWM global configuration register (PWMSET)

PWMRST: Software resets 6 groups of PWM.

0: No effect.

1: Reset the XFR registers for all PWMs, but do not reset SFRs which are required software reset.

ENPWM: PWM enable bit (including PWM0~PWM7).

0: disable PWM

1: enable PWM

19.2.2 Enhanced PWM configuration registers (PWMCFG)

PWMCBIF: The interrupt flag bit of PWM when the PWM counter returns to zero (n=0~5).

When the 15-bit PWM counter overflows and returns to zero, this bit is set by hardware automatically and an

interrupt is requested to CPU. This flag bit needs to be cleared by software.

EPWMCBI: PWM counter returns to zero interrupt enable bit. (n= 0 ~5)

Loading...

Loading...