23 DMA

STC8A8K64D4 series of microcomputers support the function of batch data storage, that is, traditional DMA.

The following DMA operations are supported:

⚫ M2M_DMA: read and write data from XRAM memory to XRAM memory

⚫ ADC_DMA: automatically scan the enabled ADC channels and automatically store the converted ADC

data into XRAM

⚫ SPI_DMA: automatically exchange data between XRAM data and SPI peripherals

⚫ UR1T_DMA: automatically send the data in XRAM through UART1

⚫ UR1R_DMA: automatically store the data received from UART1 into XRAM

⚫ UR2T_DMA: automatically send the data in XRAM through UART2

⚫ UR2R_DMA: automatically store the data received from UART2 into XRAM

⚫ UR3T_DMA: automatically send the data in XRAM through UART3

⚫ UR3R_DMA: automatically store the data received from UART3 into XRAM

⚫ UR4T_DMA: automatically send the data in XRAM through UART 4

⚫ UR4R_DMA: automatically store the data received from UART4 into XRAM

⚫ LCM_DMA: automatically exchange data between the data in XRAM and the LCM device

The maximum size of each DMA data transfer is 256 bytes.

Each DMA read and write operation to XRAM can be set to 4-level access priority, and the hardware will automatically

perform the access arbitration of the XRAM bus, which will not affect CPU access to XRAM. Under the same priority,

the access order of different DMAs to XRAM is as follows: SPI_DMA, UR1R_DMA, UR1T_DMA, UR2R_DMA,

UR2T_DMA, UR3R_DMA, UR3T_DMA, UR4R_DMA, UR4T_DMA, LCM_DMA, M2M_DMA, ADC_DMA

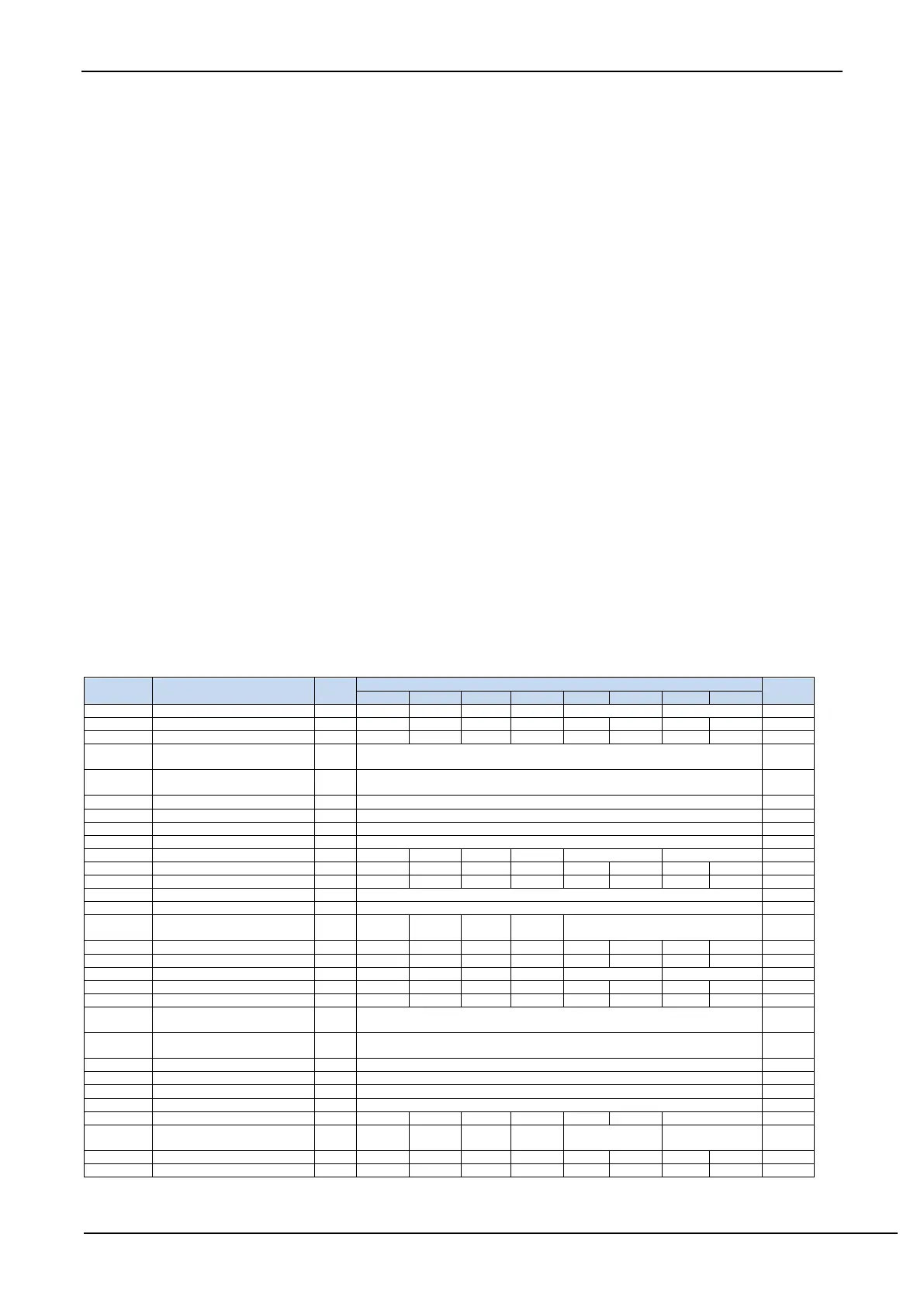

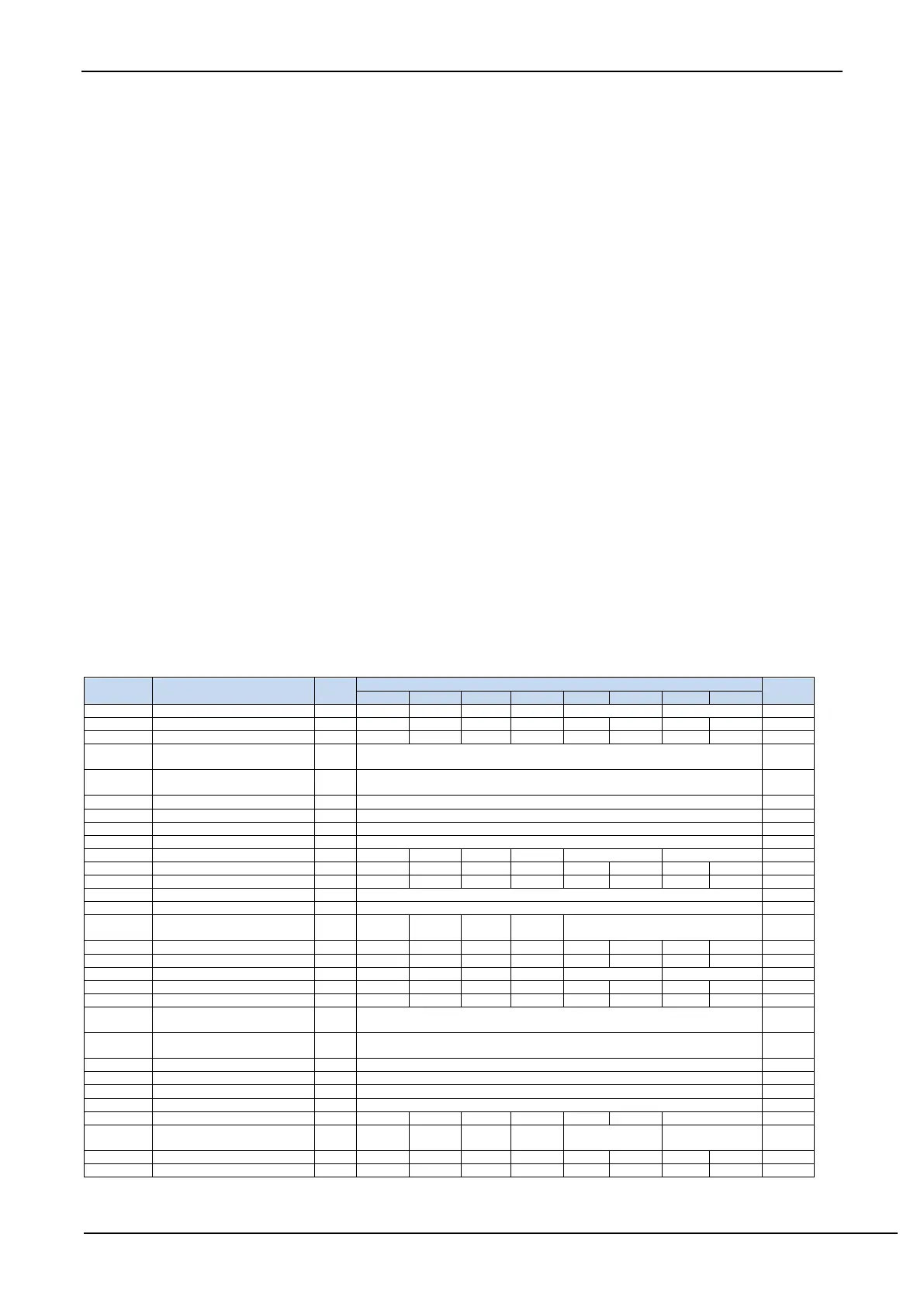

23.1 Registers Related to DMA

Loading...

Loading...