STC8A8K64D4 Series Manual

23.3 ADC Automatic Data Storage (ADC_DMA)

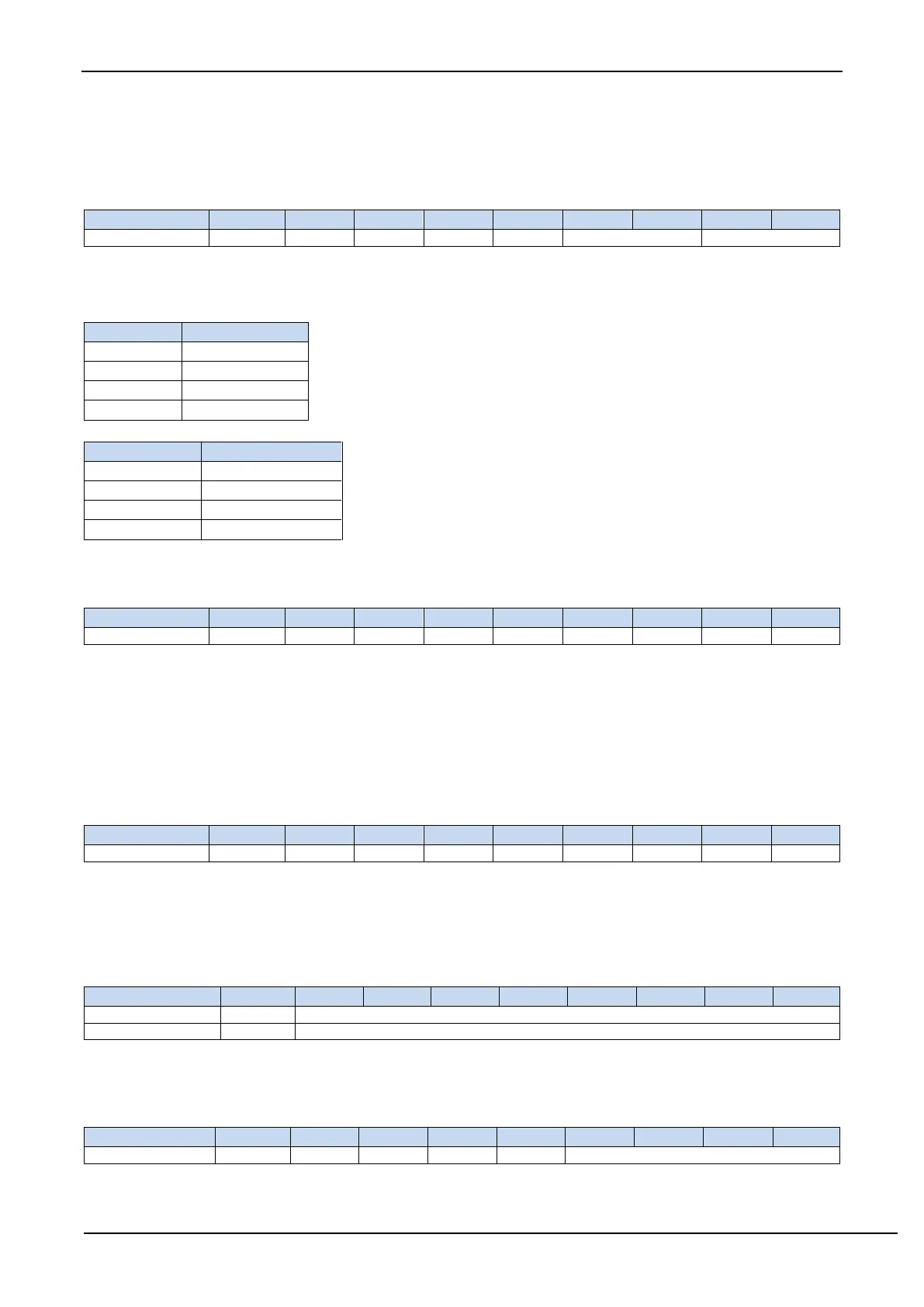

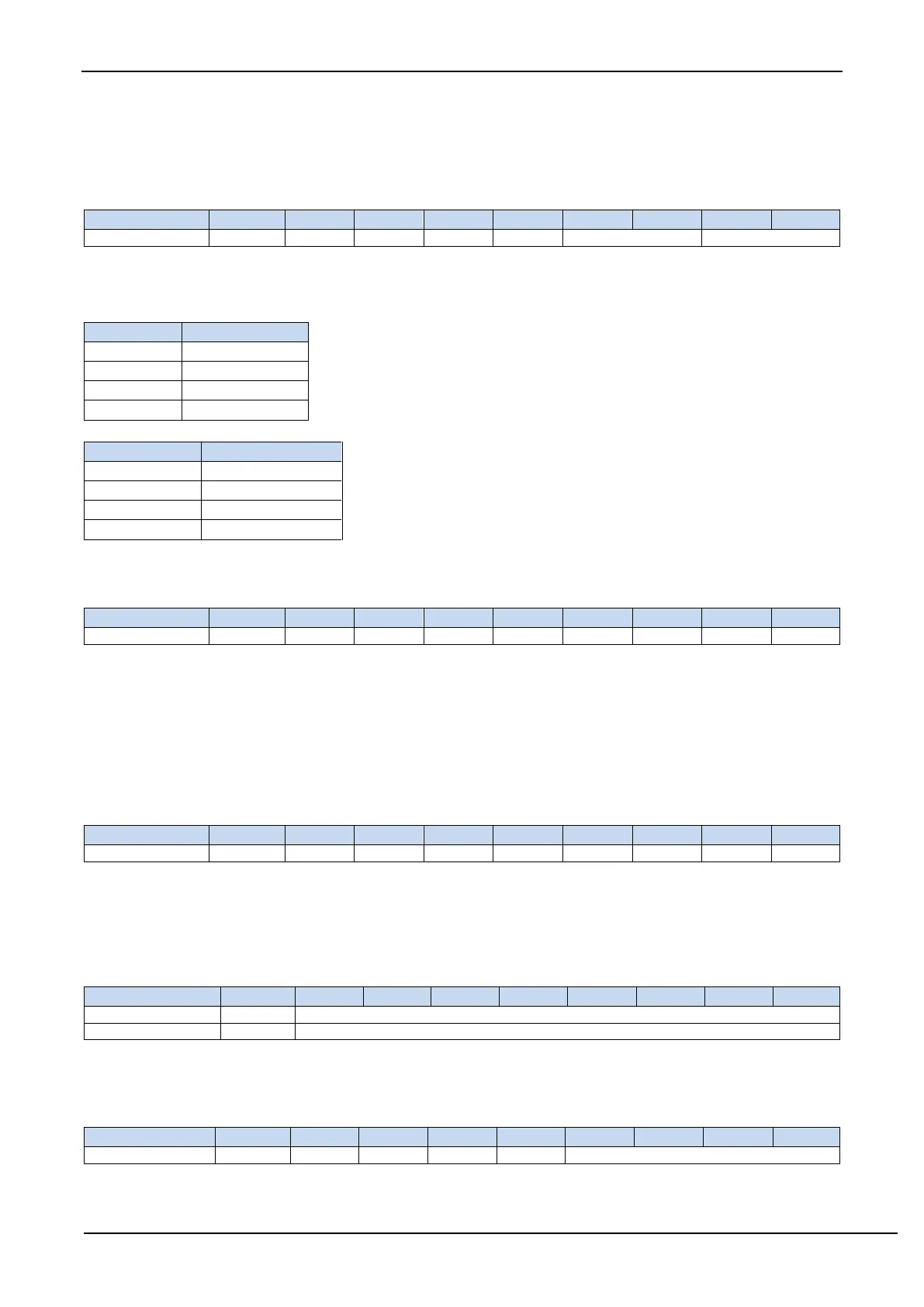

23.3.1 ADC_DMA Configuration Register (DMA_ADC_CFG)

ADCIE: ADC_DMA interrupt enable control bit

0: Disable ADC_DMA interrupt

1: Enable ADC_DMA interrupt

ADCIP[1:0]: ADC_DMA interrupt priority control bits

ADCPTY[1:0]:ADC_DMA Data bus access priority control bits

23.3.2 ADC_DMA Control Register (DMA_ADC_CR)

ENADC: ADC_DMA function enable control bit

0: Disable ADC_DMA function

1: Enable ADC_DMA function

TRIG: ADC_DMA operation trigger control bit

0: Write 0 is invalid

1: Write 1 to start ADC_DMA operation.

23.3.3 ADC_DMA Status Register (DMA_ADC_STA)

ADCIF: ADC_DMA interrupt request flag bit. After ADC_DMA completes scanning all enabled ADC channels, the

hardware automatically sets ADCIF to 1. If the ADC_DMA interrupt is enabled, the interrupt service routine is

entered. The flag bit needs to be cleared by software.

23.3.4 ADC_DMA Receive Address Registers (DMA_ADC_RXAx)

DMA_ADC_RXA: Set the storage address of ADC conversion data during ADC_DMA operation.

23.3.5 ADC_DMA Configuration Register 2 (DMA_ADC_CFG2)

CVTIMESEL[3:0]: Set the number of ADC conversions for each ADC channel during ADC_DMA operation.

Loading...

Loading...