STC8A8K64D4 Series Manual

-

Note: After the user program is reset, the system will set the initial value of this register automatically according to the

frequency division factor required for the operating frequency set during the last ISP download.

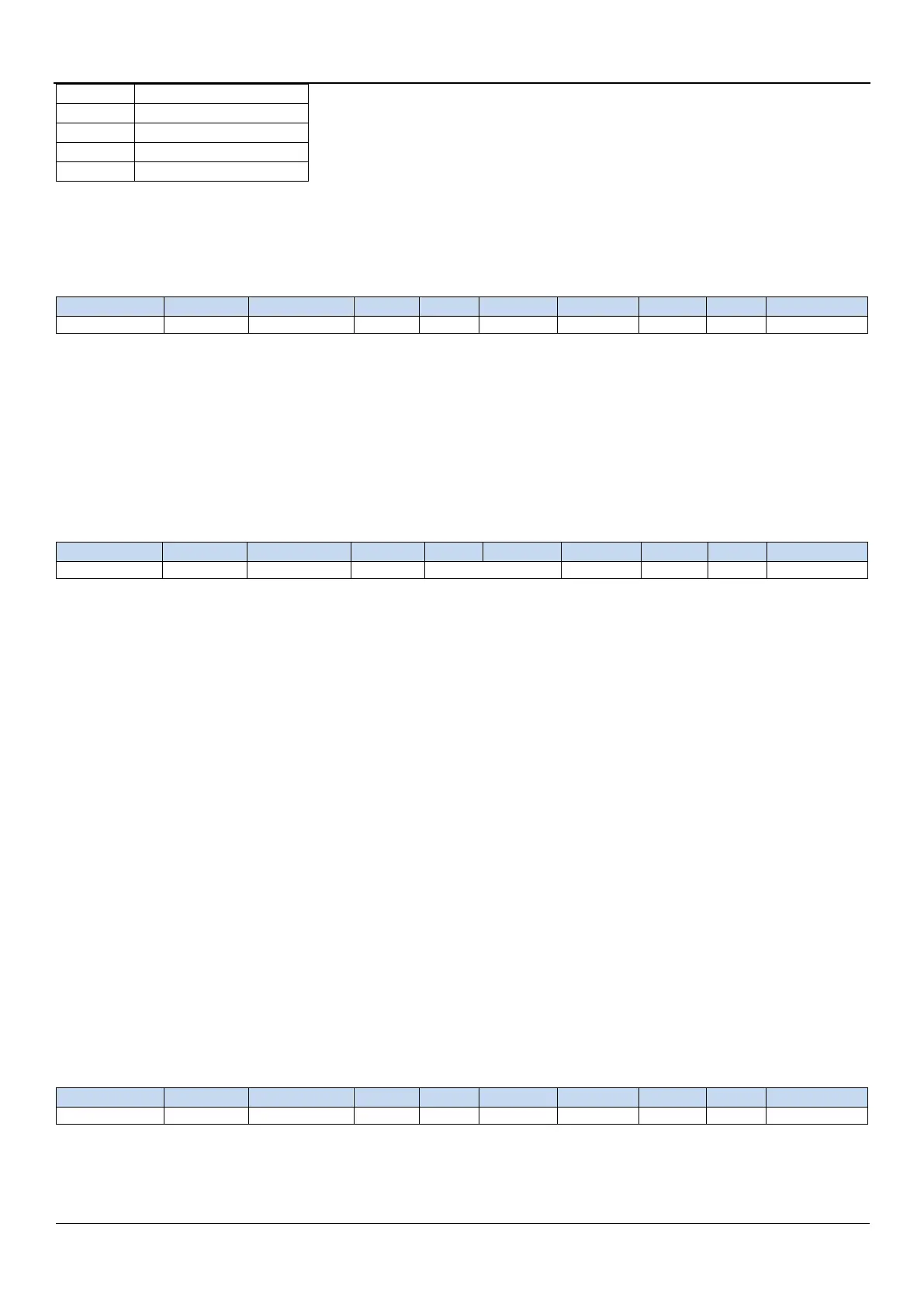

6.1.3 Internal high speed high precision IRC control register (HIRCCR)

ENHIRC: internal high speed high precision IRC enable bit

0: disable internal high-precision IRC

1: enable internal high-precision IRC

HIRCST: internal high speed high precision IRC frequency stability flag (read-only)

After the internal IRC is enabled from the stopped state, it must take some time for the frequency of the oscillator to

become stable. The clock controller will set the HIRCST flag automatically after the internal oscillator frequency stabilizes.

When the user program needs to switch the clock to internal IRC, ENHIRC must be set at first to enable the oscillator and

then keep polling the oscillator stable flag HIRCST until the flag changes to 1.

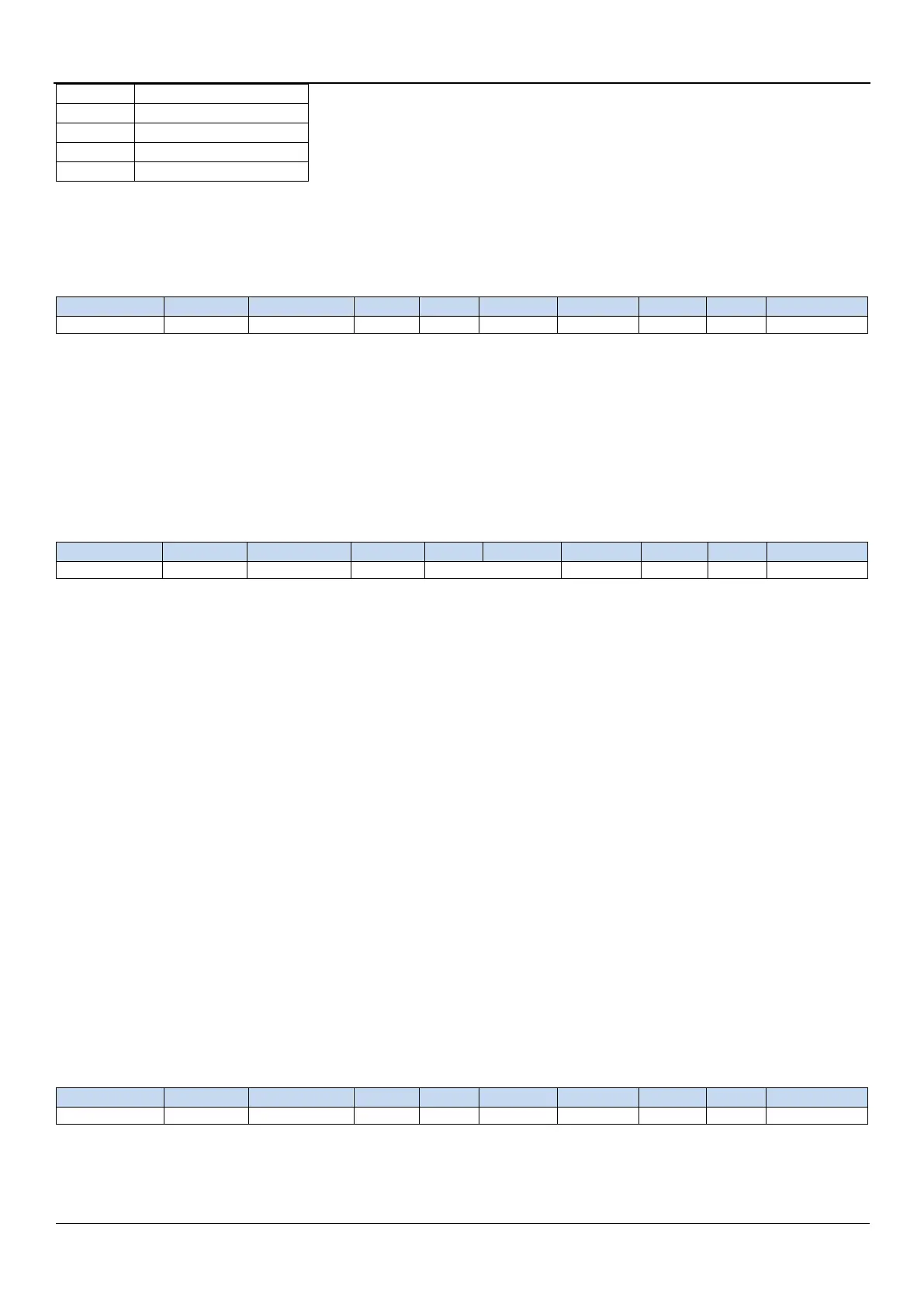

6.1.4 External Oscillator control register (XOSCCR)

ENXOSC: external oscillator enable bit

0: disable external oscillator

1: enable external oscillator

XITYPE: external clock source type

0: The external clock source is the external clock signal (or active crystal). The signal source only needs to be connected

to the XTALI(P1.7) of microcontroller. (At this time, P1.6 is fixed in high-impedance input mode, which can be used

to read external digital signals or as ADC input, but it is generally not recommended to be used, because the high-

frequency oscillation signal of the adjacent P1.7 will affect P1.6 signal.)

1: The external clock source is a crystal oscillator which is connected to XTALI (P1.7) and XTALO (P1.6) of

microcontroller.

XOSCST: external crystal oscillator frequency stability flag (read-only)

After the external crystal oscillator is enabled from the stopped state, it must take some time for the frequency of the

oscillator to become stable. The clock controller will set the XOSCST flag automatically after the oscillator frequency

stabilizes. When the user program needs to switch the clock to external crystal oscillator, ENXOSC must be set at first

to enable the oscillator and then keep polling the oscillator stable flag XOSCST until the flag changes to 1.

XCFILTER[1:0]: External crystal oscillator anti-interferencecontrol register.

00: When the external crystal oscillator frequency is 48M and below.

01: When the external crystal oscillator frequency is 24M and below

1x: When the external crystal oscillator frequency is 12M and below

NMXCG: External crystal oscillator oscillator gain control bits

0: disable oscillator gain (low gain)

1: enable oscillator gain (high gain)

6.1.5 Internal 32KHz low speed IRC control register (IRC32KCR)

ENIRC32K: internal 32KHz low speed IRC enable bit

0: disable internal 32KHz low speed IRC

1: enable internal 32KHz low speed IRC

IRC32KST: internal 32KHz low speed IRC frequency stability flag (read-only)

After the internal 32KHz low speed IRC is enabled from the stopped state, it must take some time for the frequency

Loading...

Loading...