RM0440 Rev 4 1283/2126

RM0440 General-purpose timers (TIM2/TIM3/TIM4/TIM5)

1343

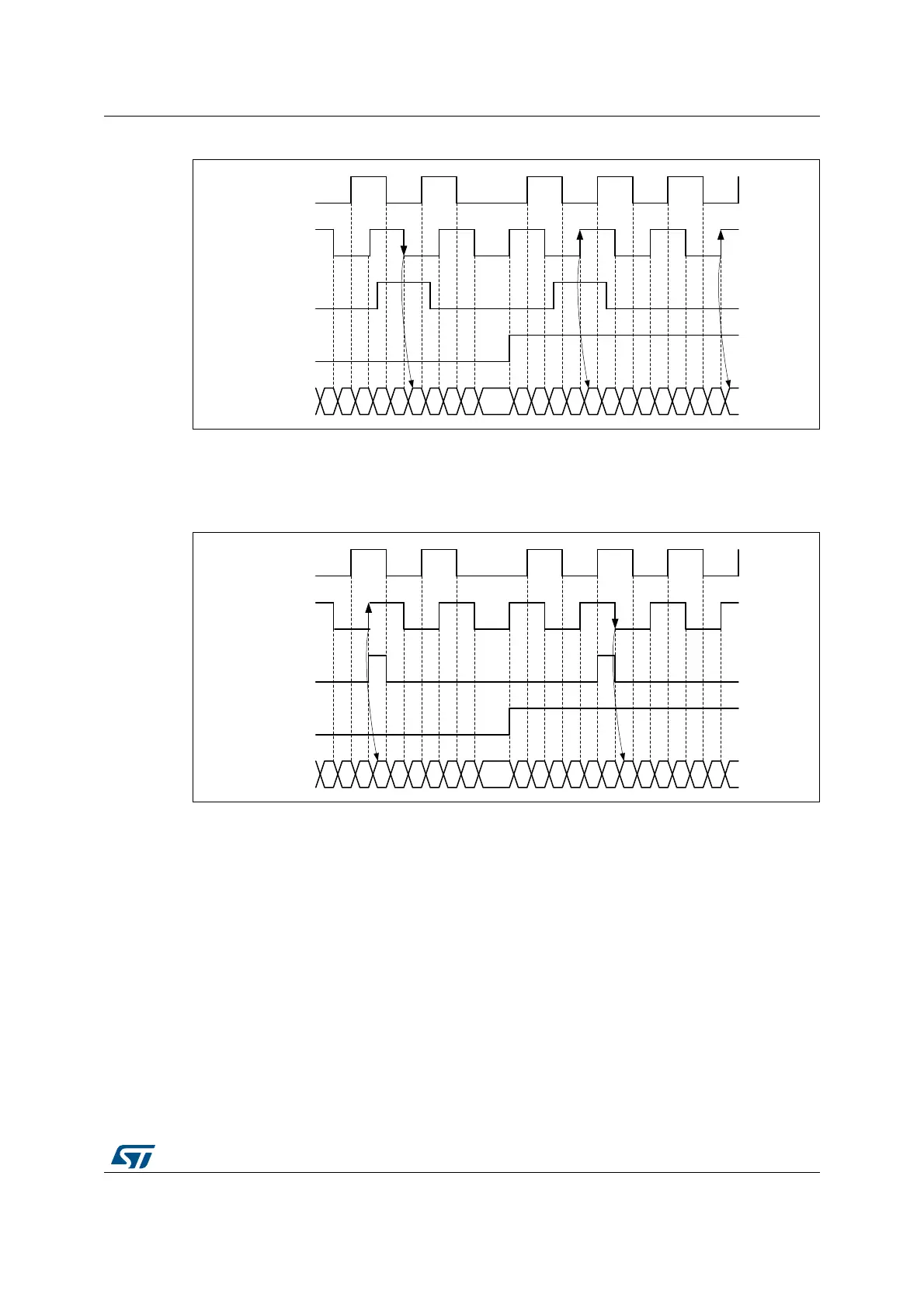

Figure 415. Counter reading with index ungated (IPOS[1:0] = 00)

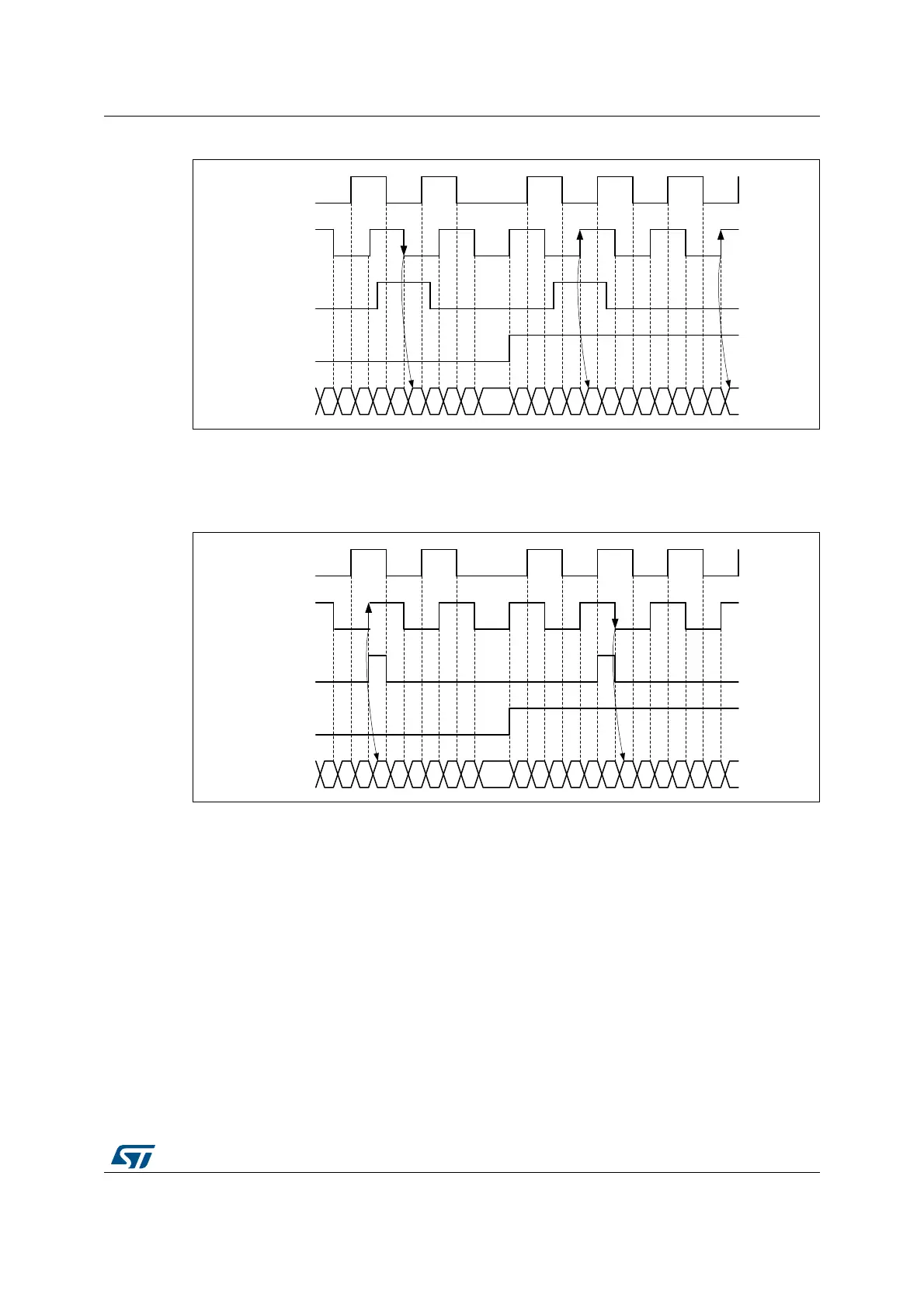

The Figure 416 below shows how the ‘gated on A & B’ mode is handled, for various pulse

alignment scenario. The arrows are indicating on which transition is the index event

generated.

Figure 416. Counter reading with index gated on channel A and B

The Figure 417 and Figure 418 detail the case where the subsequent index pulse may be

narrower than one quarter of the encoder clock period.

MSv45769V1

Channel A

Channel B

DIR bit

Index

Counter 3 4 5 6 7 0 1 2 3 4 3 2 1 0 7 6 5 4 3 2 1 0 7

MSv45770V1

Channel A

Channel B

DIR bit

Index

Counter

5 6 7 0 1 2 3 4 5 6 5 4 3 2 1 0 7 6 5 4 3 2 1

Loading...

Loading...