RM0440 Rev 4 1457/2126

RM0440 Basic timers (TIM6/TIM7)

1463

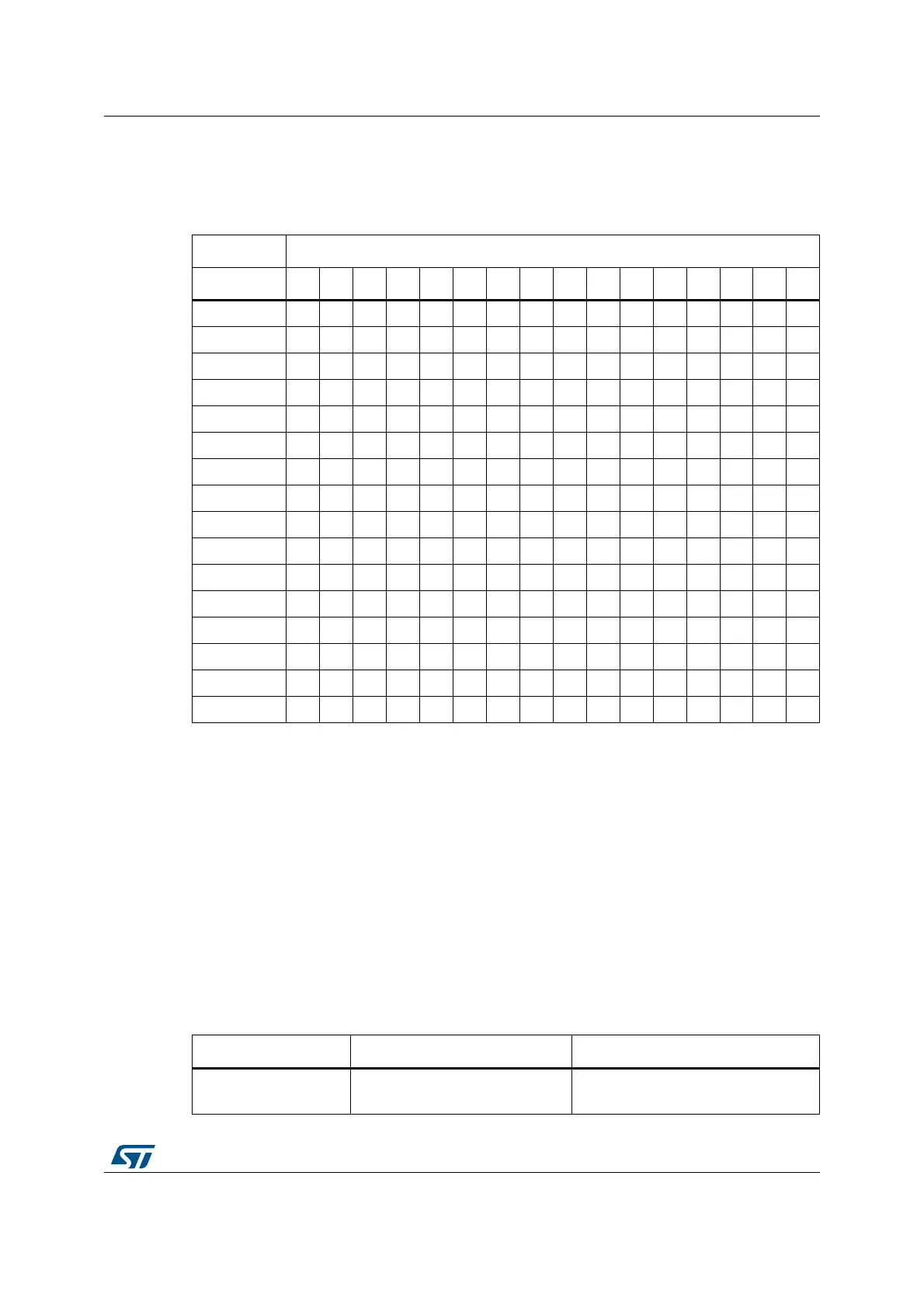

The auto-reload and compare values increments are spread following specific patterns

described in the Table 304 below. The dithering sequence is done to have increments

distributed as evenly as possible and minimize the overall ripple.

31.3.6 UIF bit remapping

The IUFREMAP bit in the TIMx_CR1 register forces a continuous copy of the Update

Interrupt Flag UIF into the timer counter register’s bit 31 (TIMxCNT[31]). This allows to

atomically read both the counter value and a potential roll-over condition signaled by the

UIFCPY flag. In particular cases, it can ease the calculations by avoiding race conditions

caused for instance by a processing shared between a background task (counter reading)

and an interrupt (Update Interrupt).

There is no latency between the assertions of the UIF and UIFCPY flags.

31.3.7 TIM6/TIM7 DMA requests

The TIM6/TIM7 can generate a single DMA request, as shown in Table 305.

Table 304. TIMx_ARR register change dithering pattern

-PWM period

LSB value12345678910111213141516

0000 ----------------

0001 +1---------------

0010 +1-------+1-------

0011 +1---+1---+1-------

0100 +1---+1---+1---+1---

0101 +1-+1-+1---+1---+1---

0110 +1 - +1 - +1 - - - +1 - +1 - +1 - - -

0111 +1 - +1 - +1 - +1 - +1 - +1 - +1 - - -

1000 +1-+1-+1-+1-+1-+1-+1-+1-

1001 +1+1+1 -+1 -+1 -+1 -+1 -+1 -+1 -

1010 +1 +1 +1 - +1 - +1 - +1 +1 +1 - +1 - +1 -

1011 +1+1+1 -+1+1+1 -+1+1+1 - +1 - +1 -

1100 +1 +1 +1 - +1 +1 +1 - +1 +1 +1 - +1 +1 +1 -

1101 +1 +1 +1 +1 +1 +1 +1 - +1 +1 +1 - +1 +1 +1 -

1110 +1+1+1+1+1+1+1 -+1+1+1+1+1+1+1 -

1111 +1 +1 +1 +1 +1 +1 +1 +1 +1 +1 +1 +1 +1 +1 +1 -

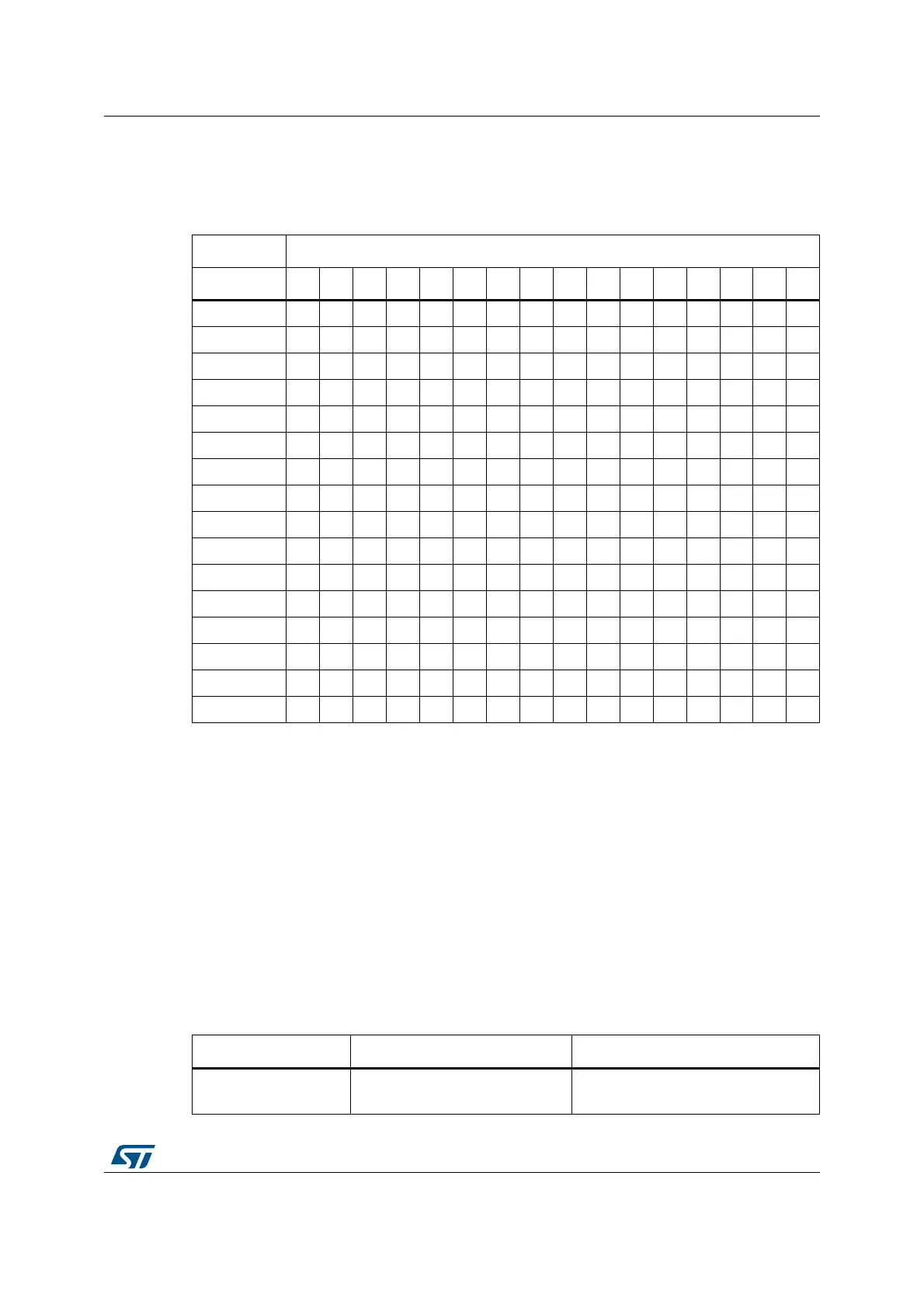

Table 305. DMA request

DMA acronym DMA request Enable control bit

TIM6_UP

TIM7_UP

Update UDE

Loading...

Loading...