General-purpose timers (TIM15/TIM16/TIM17) RM0440

1386/2126 RM0440 Rev 4

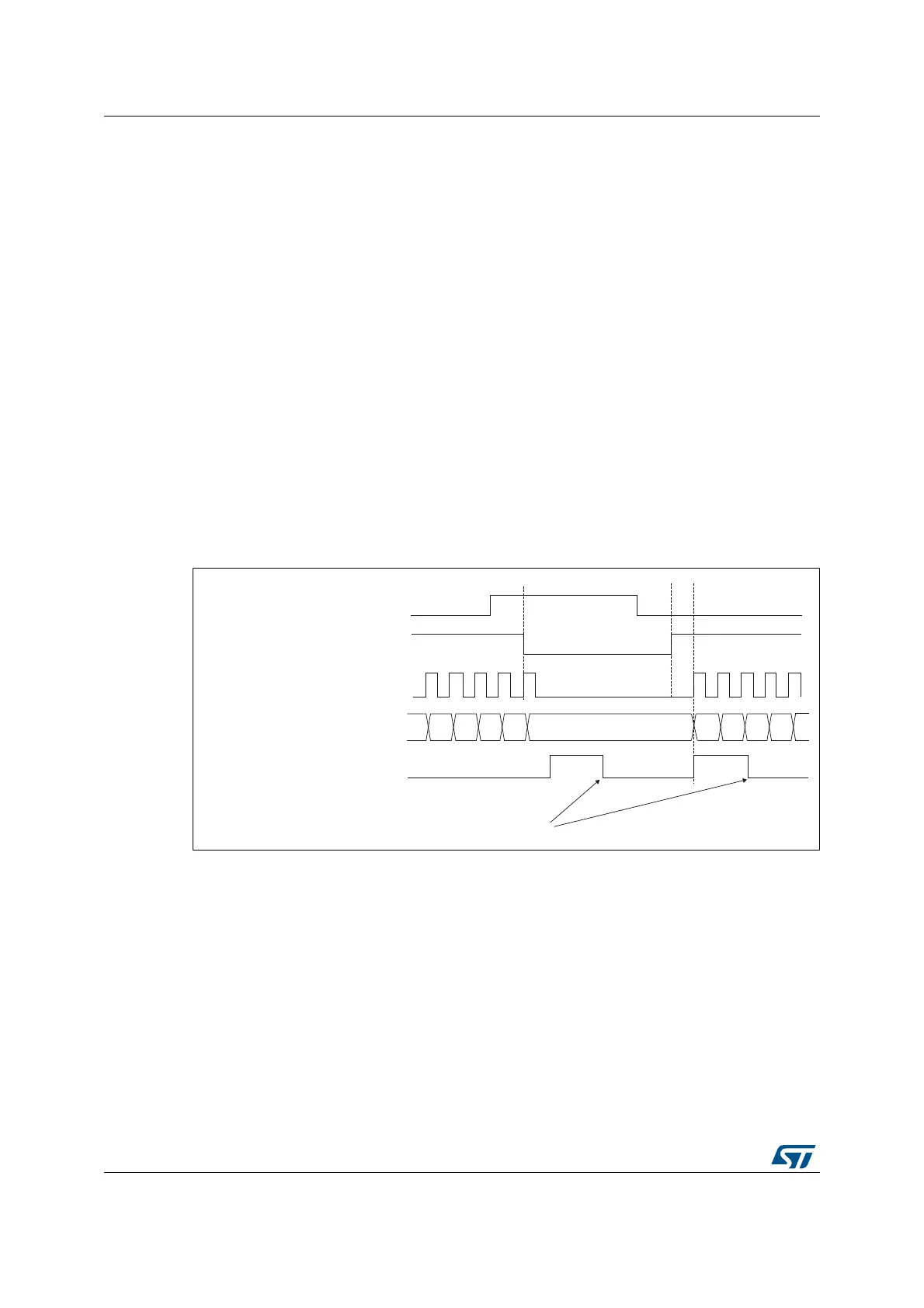

Slave mode: Gated mode

The counter can be enabled depending on the level of a selected input.

In the following example, the upcounter counts only when tim_ti1 input is low:

1. Configure the channel 1 to detect low levels on tim_ti1. Configure the input filter

duration (in this example, we do not need any filter, so we keep IC1F=0000). The

capture prescaler is not used for triggering, so it does not need to be configured. The

CC1S bits select the input capture source only, CC1S=01 in TIMx_CCMR1 register.

Write CC1P=1 and CC1NP = ‘0’ in the TIMx_CCER register to validate the polarity (and

detect low level only).

2. Configure the timer in gated mode by writing SMS=101 in TIMx_SMCR register. Select

tim_ti1 as the input source by writing TS=00101 in TIMx_SMCR register.

3. Enable the counter by writing CEN=1 in the TIMx_CR1 register (in gated mode, the

counter doesn’t start if CEN=0, whatever is the trigger input level).

The counter starts counting on the internal clock as long as tim_ti1 is low and stops as soon

as tim_ti1 becomes high. The TIF flag in the TIMx_SR register is set both when the counter

starts or stops.

The delay between the rising edge on tim_ti1 and the actual stop of the counter is due to the

resynchronization circuit on tim_ti1 input.

Figure 477. Control circuit in gated mode

MSv62362V1

37

tim_cnt_ck, tim_psc_ck

Counter register

38

32 33

34

35 36

3130

TIF

tim_ti1

CEN

Write TIF = 0

Loading...

Loading...