RM0440 Rev 4 183/2126

RM0440 Embedded Flash memory (FLASH) for category 4 devices

228

4.7.10 Flash PCROP1 End address register (FLASH_PCROP1ER)

Address offset: 0x28

Reset value: 0xX000 XXXX. Register bits are loaded with values from Flash memory at

OBL.

Access: no wait state when no Flash memory operation is on going, word, half-word access.

PCROP_RDP bit can be accessed with byte access.

4.7.11 Flash WRP area A address register (FLASH_WRP1AR)

Address offset: 0x2C

Reset value: 0x00XX 00XX. Register bits are loaded with values from Flash memory at

OBL.

Access: no wait state when no Flash memory operation is on going, word, half-word and

byte access

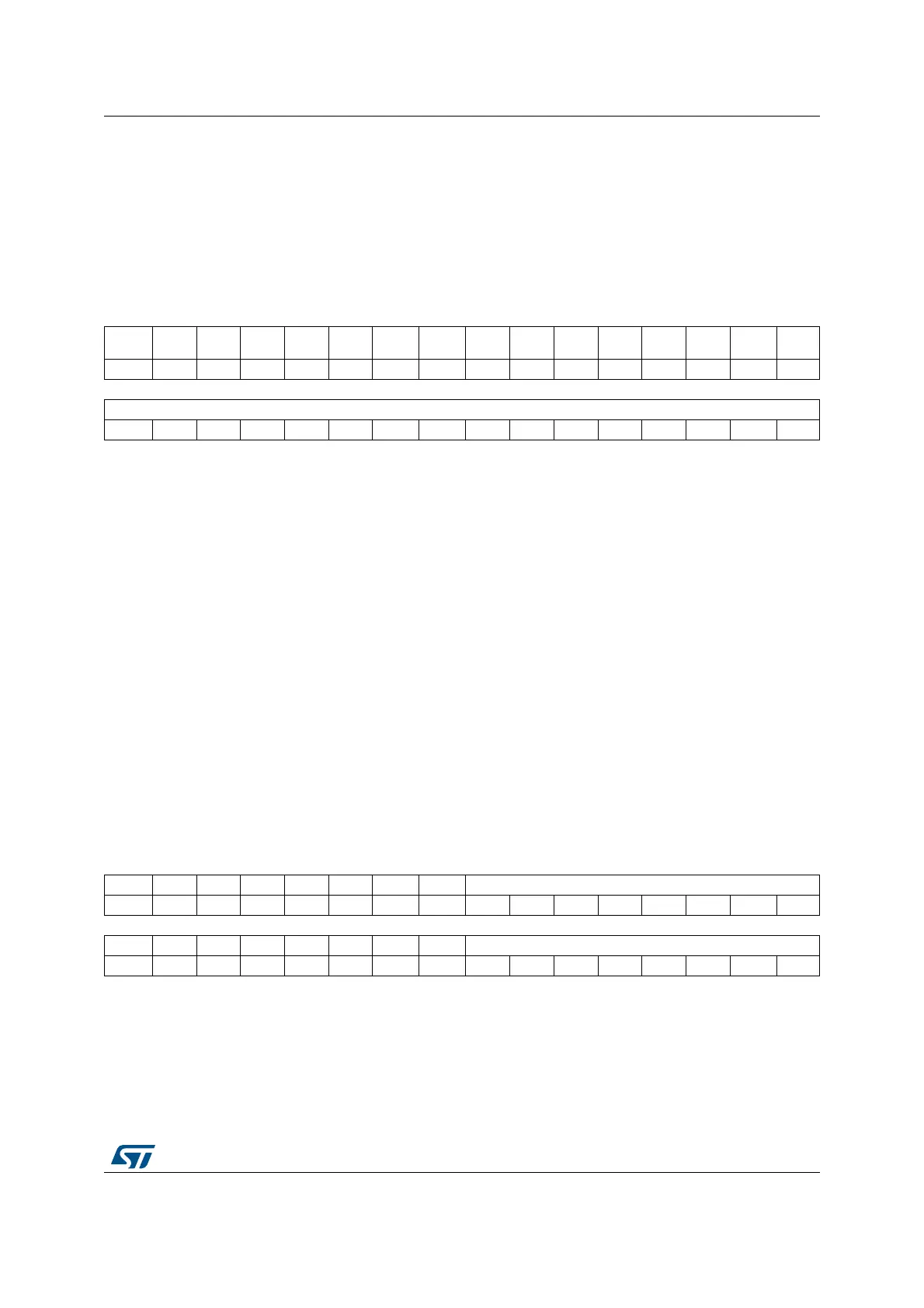

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

PCROP

_RDP

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

rs

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

PCROP1_END[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bit 31 PCROP_RDP: PCROP area preserved when RDP level decreased

This bit is set only. It is reset after a full mass erase due to a change of RDP

from Level 1 to Level 0.

0: PCROP area is not erased when the RDP level is decreased from Level 1 to

Level 0.

1: PCROP area is erased when the RDP level is decreased from Level 1 to

Level 0 (full mass erase).

Bits 30:16 Reserved, must be kept cleared

Bits 15:0 PCROP1_END: PCROP area end offset

PCROP1_END contains the last double-word of the PCROP area.

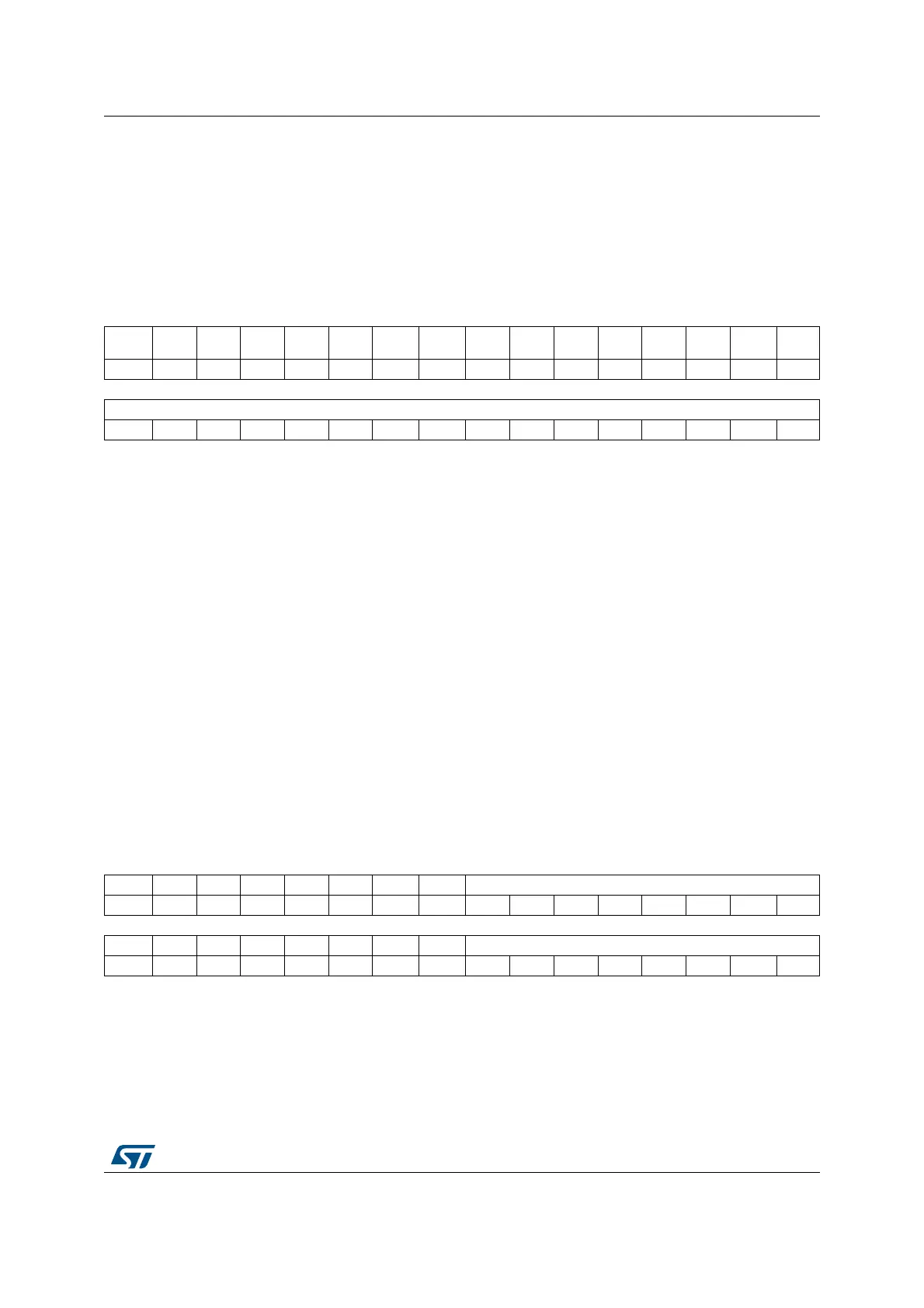

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. WRP1A_END[7:0]

rw rw rw rw rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. WRP1A_STRT[7:0]

rw rw rw rw rw rw rw rw

Bits 31:24 Reserved, must be kept cleared

Loading...

Loading...