High-resolution timer (HRTIM) RM0440

868/2126 RM0440 Rev 4

match (DELCMPx[1:0]= 10) or a compare 3 match (DELCMPx[1:0]= 11) to have a

timeout function if capture 1/2 event is missing.

When the capture occurs, the comparison is done with the (HRTIM_CMP2/4xR +

HRTIM_CPT1/2xR) value. If no capture is triggered within the period, the behavior depends

on the DELCMPx[1:0] value:

• DELCMPx[1:0] = 01: the compare event is not generated

• DELCMPx[1:0] = 10 or 11: the comparison is done with the sum of the 2 compares (for

instance HRTIM_CMP2xR + HRTIM_CMP1xR). The captures are not taken into

account if they are triggered after CMPx + CMP1 (resp. CMPx + CMP3).

The captures are enabled again at the beginning of the next PWM period.

If the result of the auto-delayed summation is above 0xFFFF (overflow), the value is ignored

and no compare event is generated until a new period is started.

Note: DELCMPx[1:0] bitfield must be reset when reprogrammed from one value to the other to re-

initialize properly the auto-delayed mechanism, for instance:

• DELCMPx[1:0] = 10

• DELCMPx[1:0] = 00

• DELCMPx[1:0] = 11

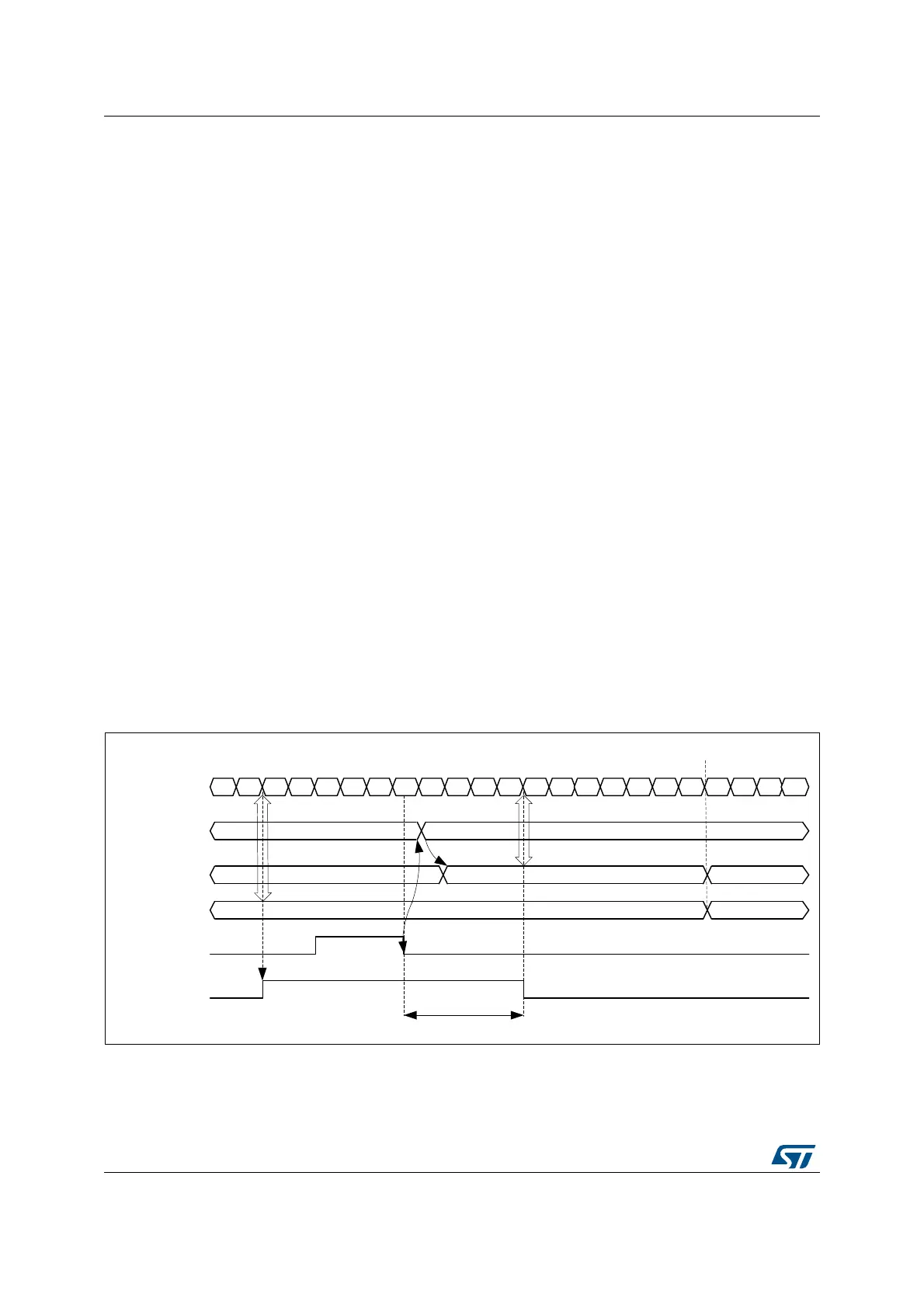

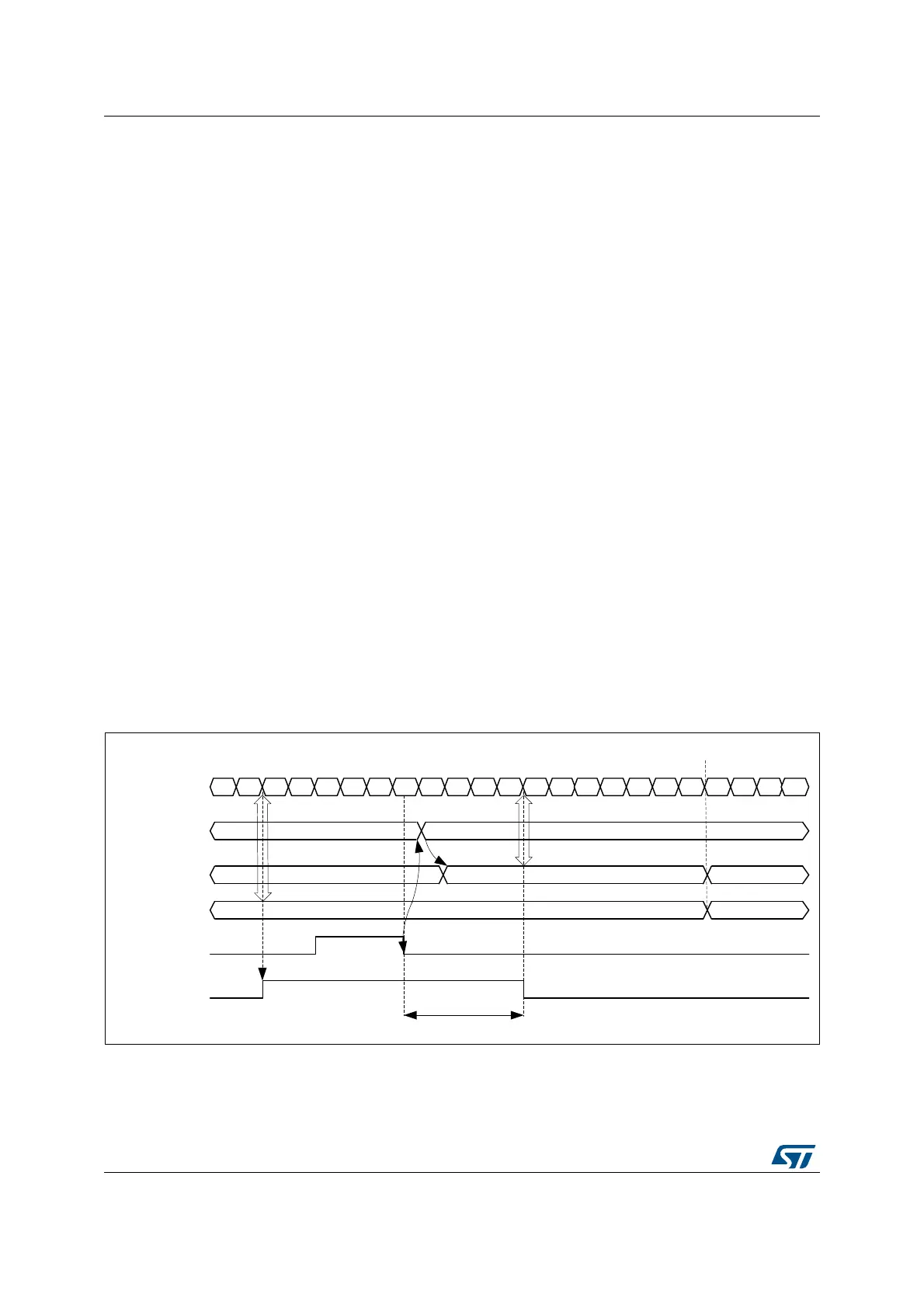

As an example, Figure 193 shows how the following signal is generated:

• Output set when the counter is equal to compare 1 value

• Output reset 5 cycles after a falling edge on a given external event

Note: To simplify the figure, the high-resolution is not used in this example (CKPSC[2:0] = 101),

thus the counter is incremented at the f

HRTIM

rate. Similarly, the external event signal is

shown without any resynchronization delay: practically, there is a delay of 1 to 2 f

HRTIM

clock

periods between the falling edge and the capture event due to an internal resynchronization

stage which is necessary to process external input signals.

Figure 193. Auto-delayed compare

A regular compare channel (e.g. compare 1) is used for the output set: as soon as the

counter matches the content of the compare register, the output goes to its active state.

MSv48374V1

Counter

HRTIM_CPT1xR

External event

1 2 3 4 5 6 70 9 10 11 12 138 14 15 16 18 0 1 2 317

Previous

7

HRTIM_CMP2xR

HRTIM_CMP1xR

Preload=5 Active: disabled

25

Output

Match

Match

Capture

Preload=5 Active=12

Preload=8

Active: disabled

~5 cycles

Update

Loading...

Loading...