General-purpose timers (TIM15/TIM16/TIM17) RM0440

1350/2126 RM0440 Rev 4

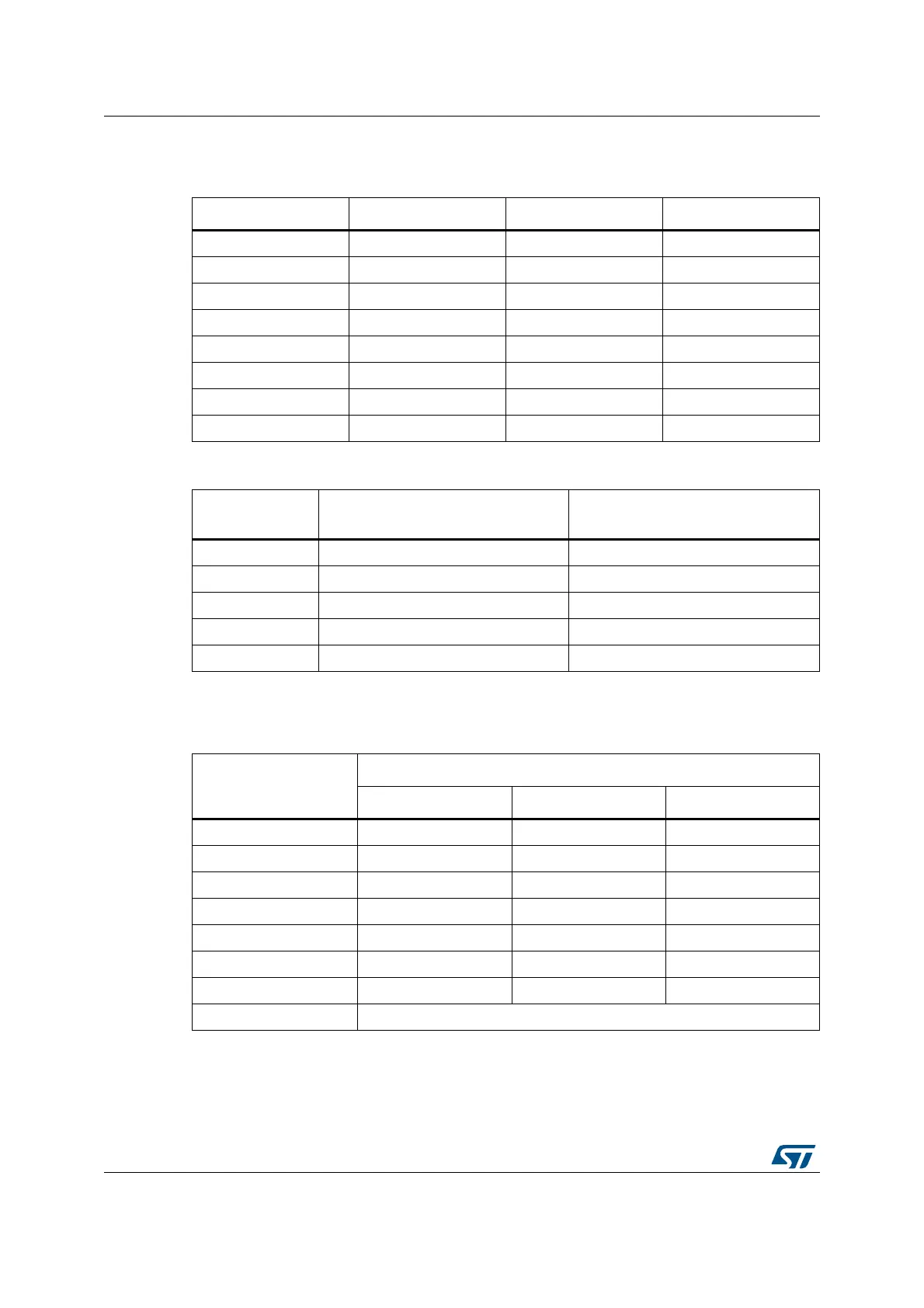

Table 291 and Table 292 list the sources connected to the tim_brk input.

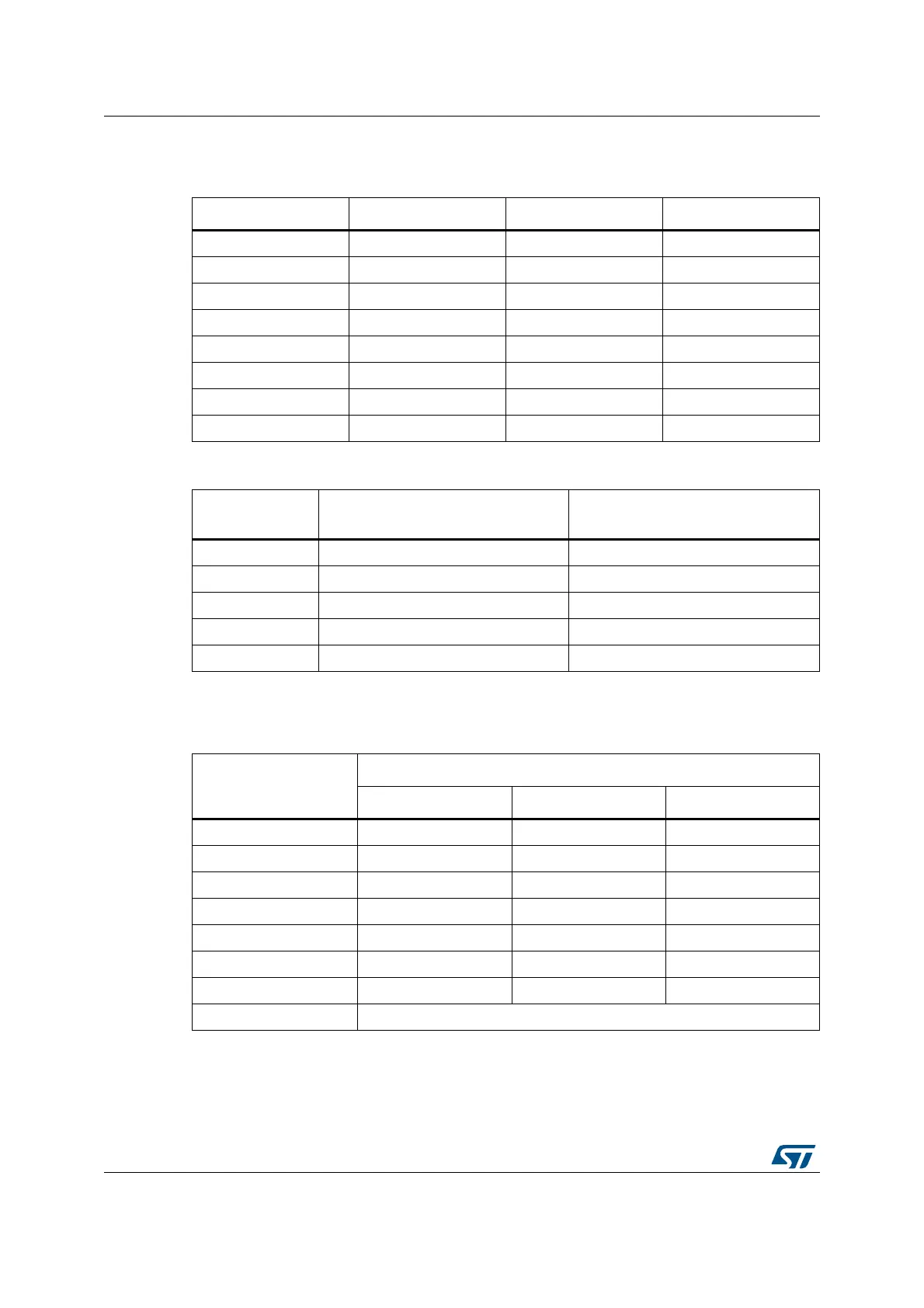

Table 293 lists the internal sources connected to the tim_ocref_clr input multiplexer.

Table 291. Timer break interconnect

tim_brk inputs TIM15 TIM16 TIM17

TIM_BKIN TIM15_BKIN pin TIM16_BKIN pin TIM17_BKIN pin

tim_brk_cmp1 comp1_out comp1_out comp1_out

tim_brk_cmp2 comp2_out comp2_out comp2_out

tim_brk_cmp3 comp3_out comp3_out comp3_out

tim_brk_cmp4 comp4_out comp4_out comp4_out

tim_brk_cmp5 comp5_out comp5_out comp5_out

tim_brk_cmp6 comp6_out comp6_out comp6_out

tim_brk_cmp7 comp7_out comp7_out comp7_out

Table 292. System break interconnect

tim_sys_brk

inputs

TIM15 / TIM16 / TIM17

Enable bit in SYSCFG_CFGR2

register

tim_sys_brk0 Cortex

®

-M4 with FPU LOCKUP CLL

tim_sys_brk1 Programmable Voltage Detector (PVD) PVDL

tim_sys_brk2 SRAM parity error SPL

tim_sys_brk3 Flash ECC error ECCL

tim_sys_brk4 Clock Security System (CSS) None (always enabled)

Table 293. Interconnect to the ocref_clr input multiplexer

Timer OCREF clear

signal

Timer OCREF clear signals assignment

TIM15 TIM16 TIM17

tim_ocref_clr0 comp1_out comp1_out comp1_out

tim_ocref_clr1 comp2_out comp2_out comp2_out

tim_ocref_clr2 comp3_out comp3_out comp3_out

tim_ocref_clr3 comp4_out comp4_out comp4_out

tim_ocref_clr4 comp5_out comp5_out comp5_out

tim_ocref_clr5 comp6_out comp6_out comp6_out

tim_ocref_clr6 comp7_out comp7_out comp7_out

tim_ocref_clr7 Reserved

Loading...

Loading...