RM0440 Rev 4 1823/2126

RM0440 Serial audio interface (SAI)

1858

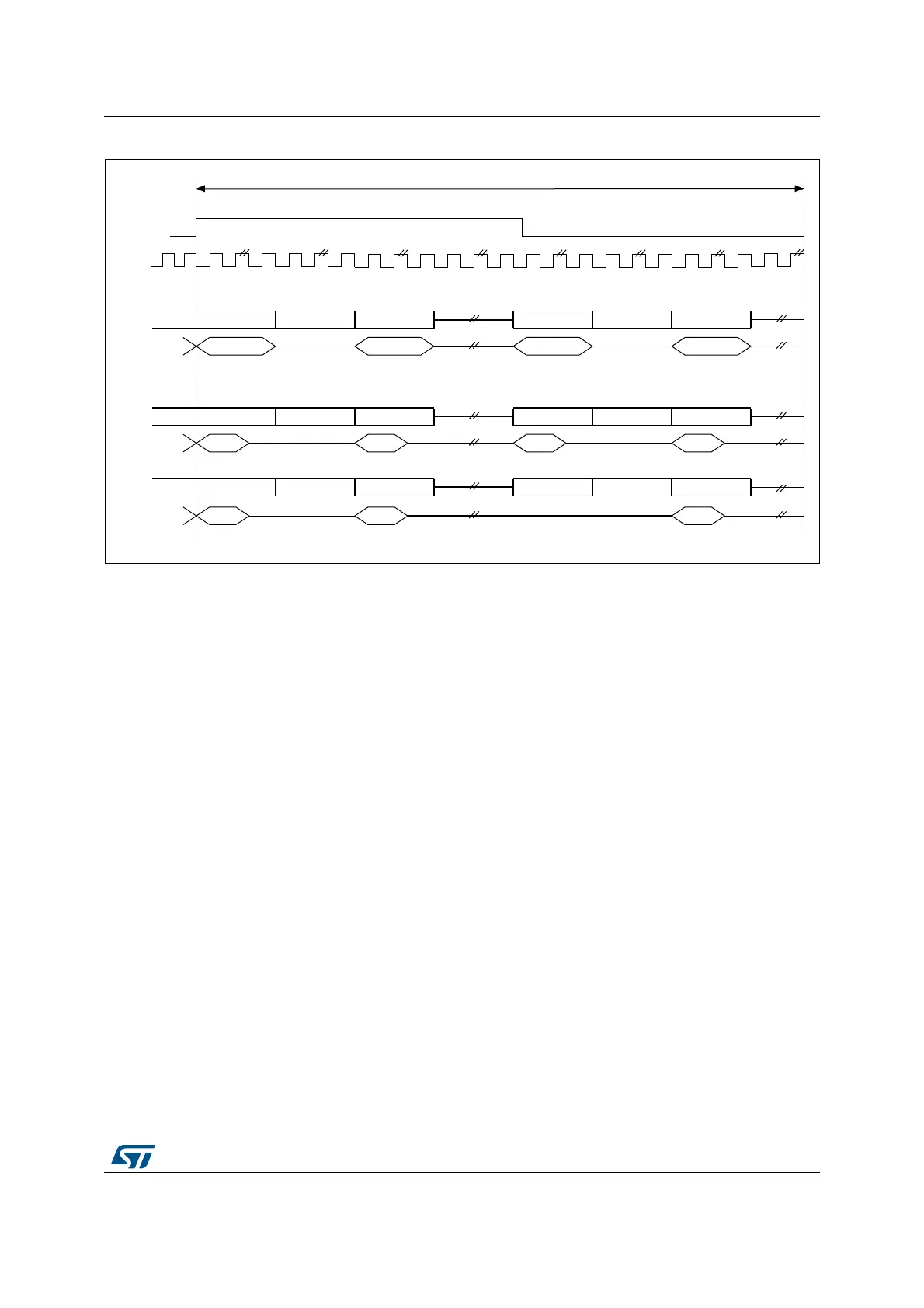

Figure 626. Tristate on output data line in a protocol like I2S

If the TRIS bit in the SAI_xCR2 register is cleared, all the High impedance states on the SD

output line on Figure 625 and Figure 626 are replaced by a drive with a value of 0.

40.3.14 Error flags

The SAI implements the following error flags:

• FIFO overrun/underrun

• Anticipated frame synchronization detection

• Late frame synchronization detection

• Codec not ready (AC’97 exclusively)

• Wrong clock configuration in master mode.

FIFO overrun/underrun (OVRUDR)

The FIFO overrun/underrun bit is called OVRUDR in the SAI_xSR register.

The overrun or underrun errors share the same bit since an audio block can be either

receiver or transmitter and each audio block in a given SAI has its own SAI_xSR register.

Overrun

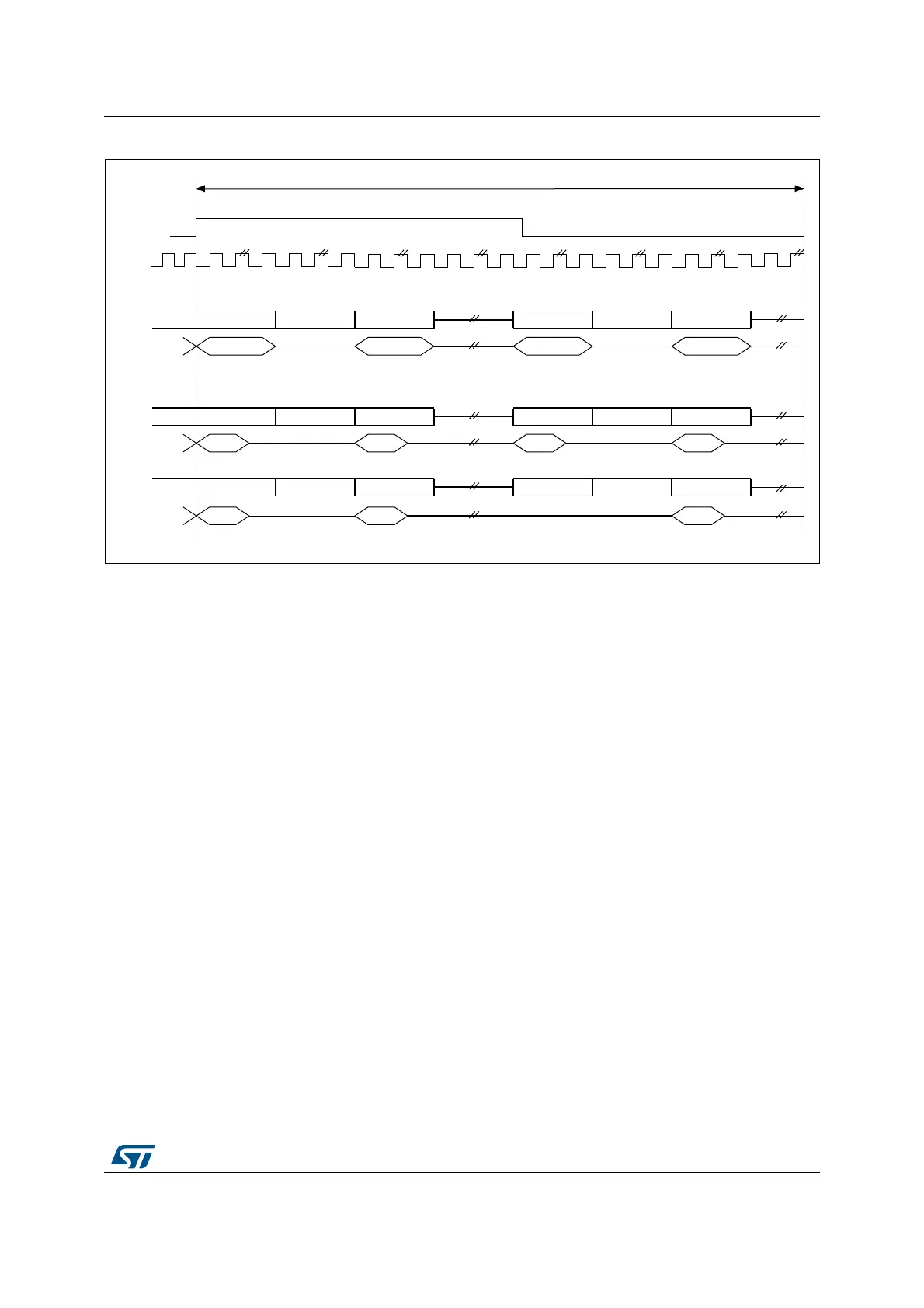

When the audio block is configured as receiver, an overrun condition may appear if data are

received in an audio frame when the FIFO is full and not able to store the received data. In

this case, the received data are lost, the flag OVRUDR in the SAI_xSR register is set and an

interrupt is generated if OVRUDRIE bit is set in the SAI_xIM register. The slot number, from

which the overrun occurs, is stored internally. No more data will be stored into the FIFO until

it becomes free to store new data. When the FIFO has at least one data free, the SAI audio

block receiver will store new data (from new audio frame) from the slot number which was

stored internally when the overrun condition was detected. This avoids data slot de-

alignment in the destination memory (refer to Figure 627).

slot

MS192346V1

Slot size = data size

Slot size > data size

SD (output)

sck

Slot 0 ON Slot 1 OFF Slot 2 ON

Slot 3 ON Slot 4 OFF Slot 5 ON

Data 0 Data 1

Slot 0 ON Slot 1 OFF Slot 2 ON

Data 0

slot

SD (output)

Data 2 Data 3

Slot 3 ON Slot 4 OFF Slot 5 ON

Data 1 Data 2 Data 3

Slot 0 ON Slot 1 OFF Slot 2 ON

Data 0

slot

SD (output)

Slot 3 ON Slot 4 OFF Slot 5 ON

Data 1 Data m

Loading...

Loading...