RM0440 Rev 4 797/2126

RM0440 Operational amplifiers (OPAMP)

829

the VPS_SEL and VMS_SEL bit fields in the OPAMP timer controlled mode register. If the

TxCMEN bit is cleared, the selection is done using the VP_SEL and VM_SEL bit fields in the

OPAMP control/status register.

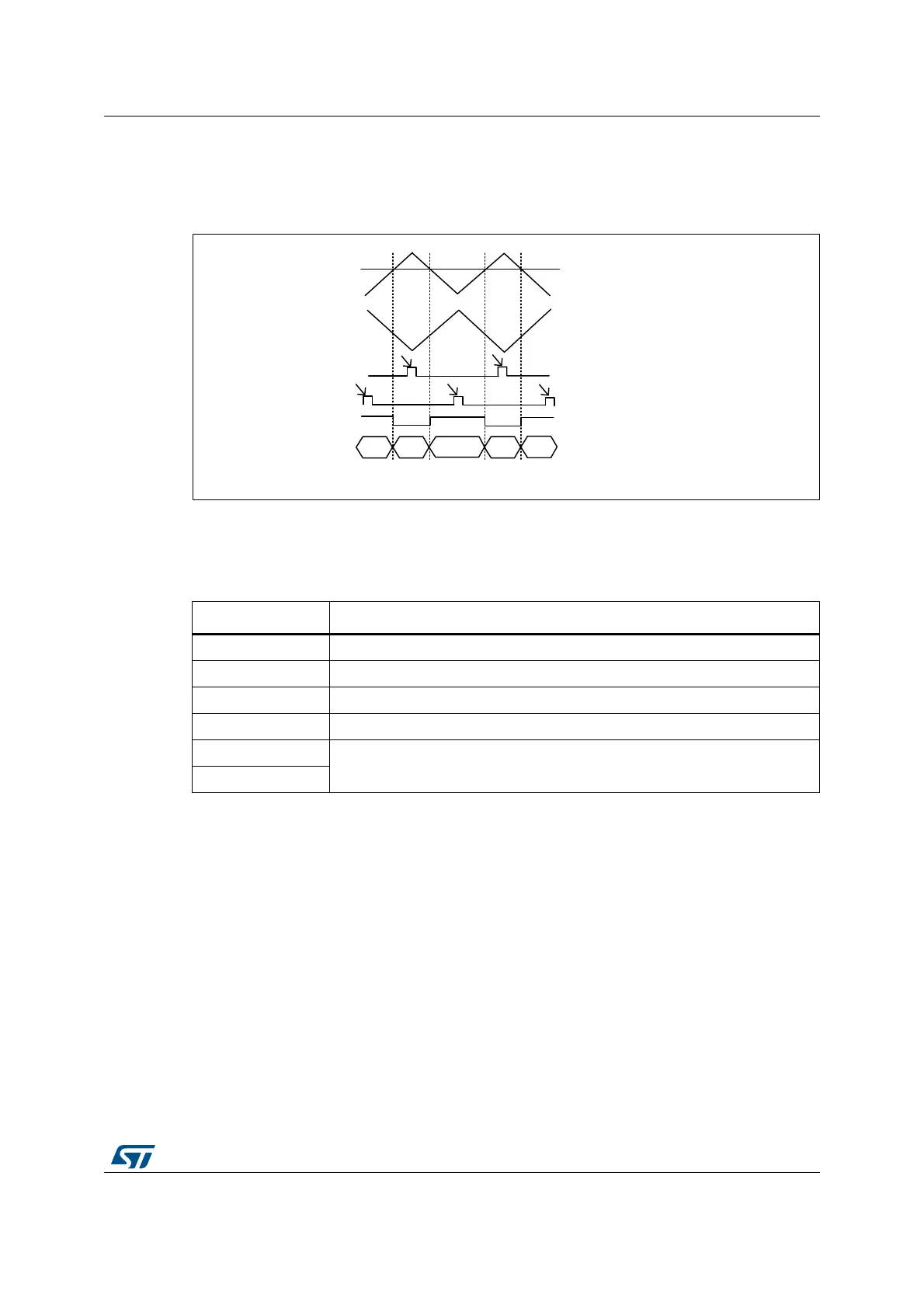

Figure 178. Timer controlled Multiplexer mode

25.4 OPAMP low-power modes

MS192230V3

CCR6

T1 counter

T8 counter

T1 output (1 out of 3)

T8 output (1 out of 3)

T1 CC6 output arriving on OPAMP input mux

OPAMP input selection:

Def = default OPAMP input selection

Sec = secondary OPAMP input selection

ADC sampling points

Sec

Def

Sec

Sec

Def

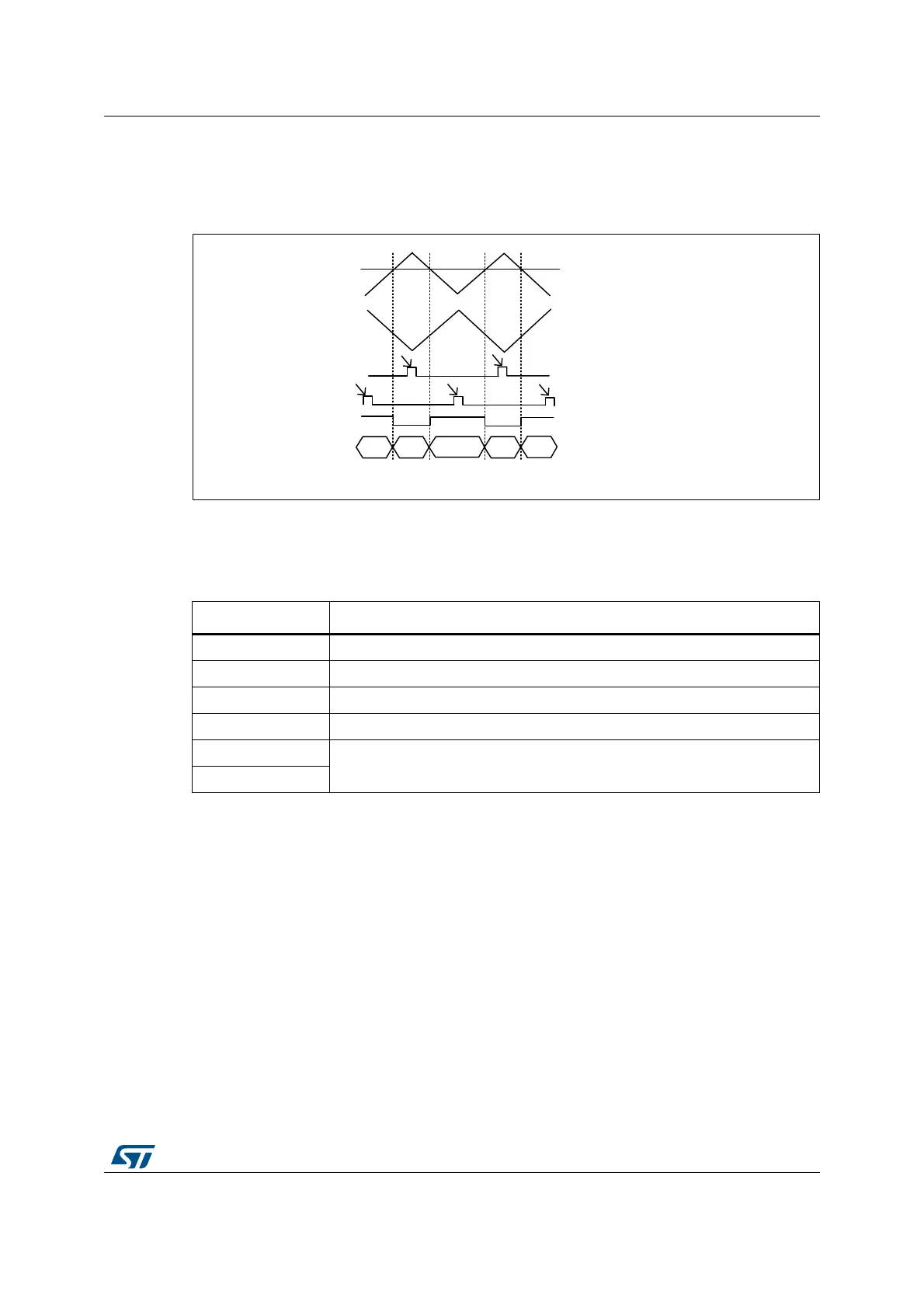

Table 202. Effect of low-power modes on the OPAMP

Mode Description

Sleep No effect.

Low-power run No effect.

Low-power sleep No effect.

Stop 0 / Stop 1 No effect, OPAMP registers content is kept.

Standby

The OPAMP registers are powered down and must be re-initialized after

exiting Standby or Shutdown mode.

Shutdown

Loading...

Loading...