RM0440 Rev 4 427/2126

RM0440 DMA request multiplexer (DMAMUX)

440

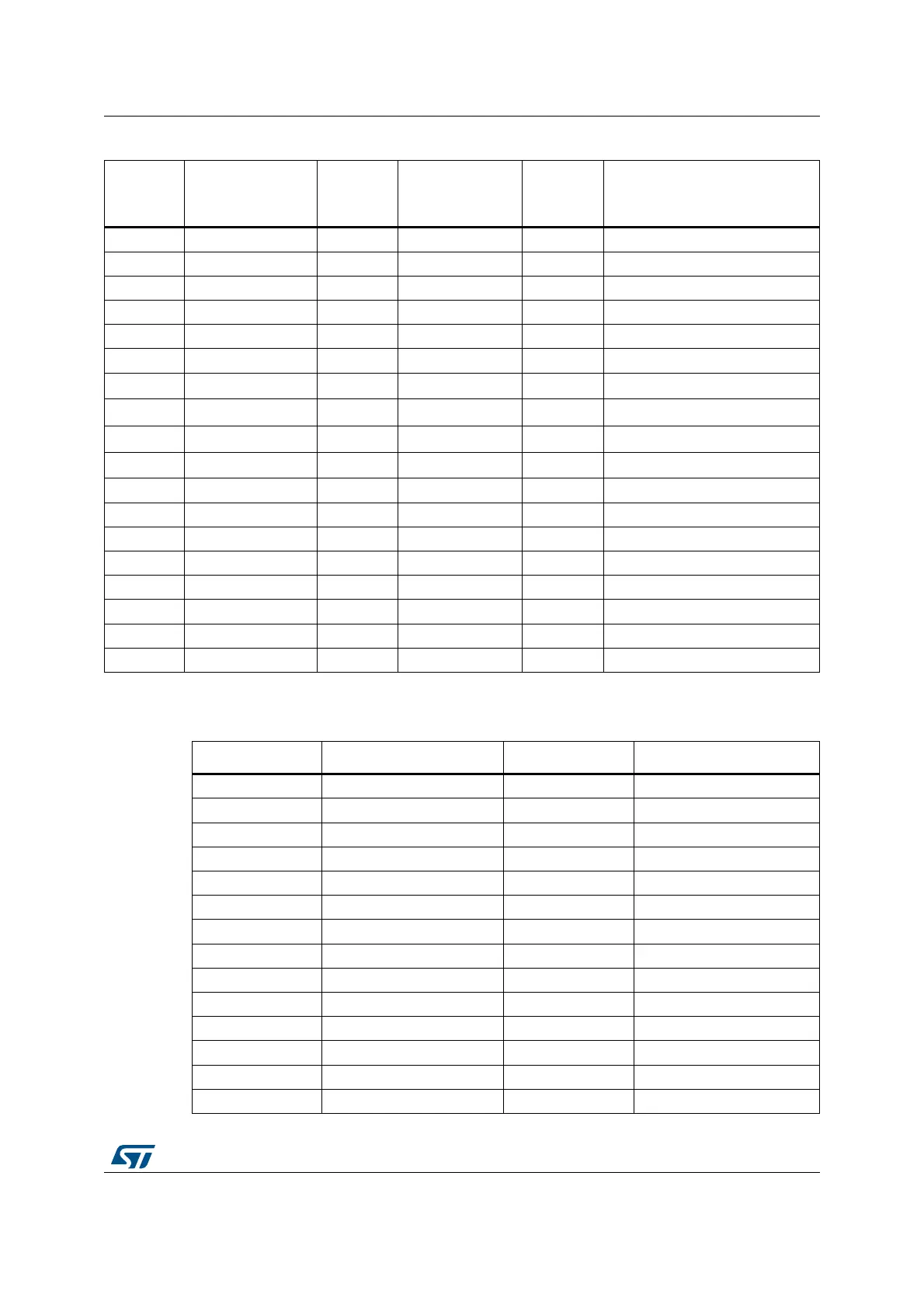

26 USART2_RX 69 TIM4_CH3 112 Cordic_Read

27 USART2_TX 70 TIM4_CH4 113 Cordic_Write

28 USART3_RX 71 TIM4_UP 114 UCPD1_RX

29 USART3_TX 72 TIM5_CH1 115 UCPD1_TX

30 UART4_RX 73 TIM5_CH2 116 Reserved

31 UART4_TX 74 TIM5_CH3 117 Reserved

32 UART5_RX 75 TIM5_CH4 118 Reserved

33 UART5_TX 76 TIM5_UP 119 Reserved

34 LPUART1_RX 77 TIM5_TRIG 120 Reserved

35 LPUART1_TX 78 TIM15_CH1 121 Reserved

36 ADC2 79 TIM15_UP 122 Reserved

37 ADC3 80 TIM15_TRIG 123 Reserved

38 ADC4 81 TIM15_COM 124 Reserved

39 ADC5 82 TIM16_CH1 125 Reserved

40 QUADSPI 83 TIM16_UP 126 Reserved

41 DAC2_CH1 84 TIM17_CH1 127 Reserved

42 TIM1_CH1 85 TIM17_UP - -

43 TIM1_CH2 86 TIM20_CH1 - -

1. See Table 2: Product specific features for available resources.

Table 91. DMAMUX: assignment of multiplexer inputs to resources

(1)

(continued)

DMA

request

MUX input

Resource

DMA

request

MUX input

Resource

DMA

request

MUX input

Resource

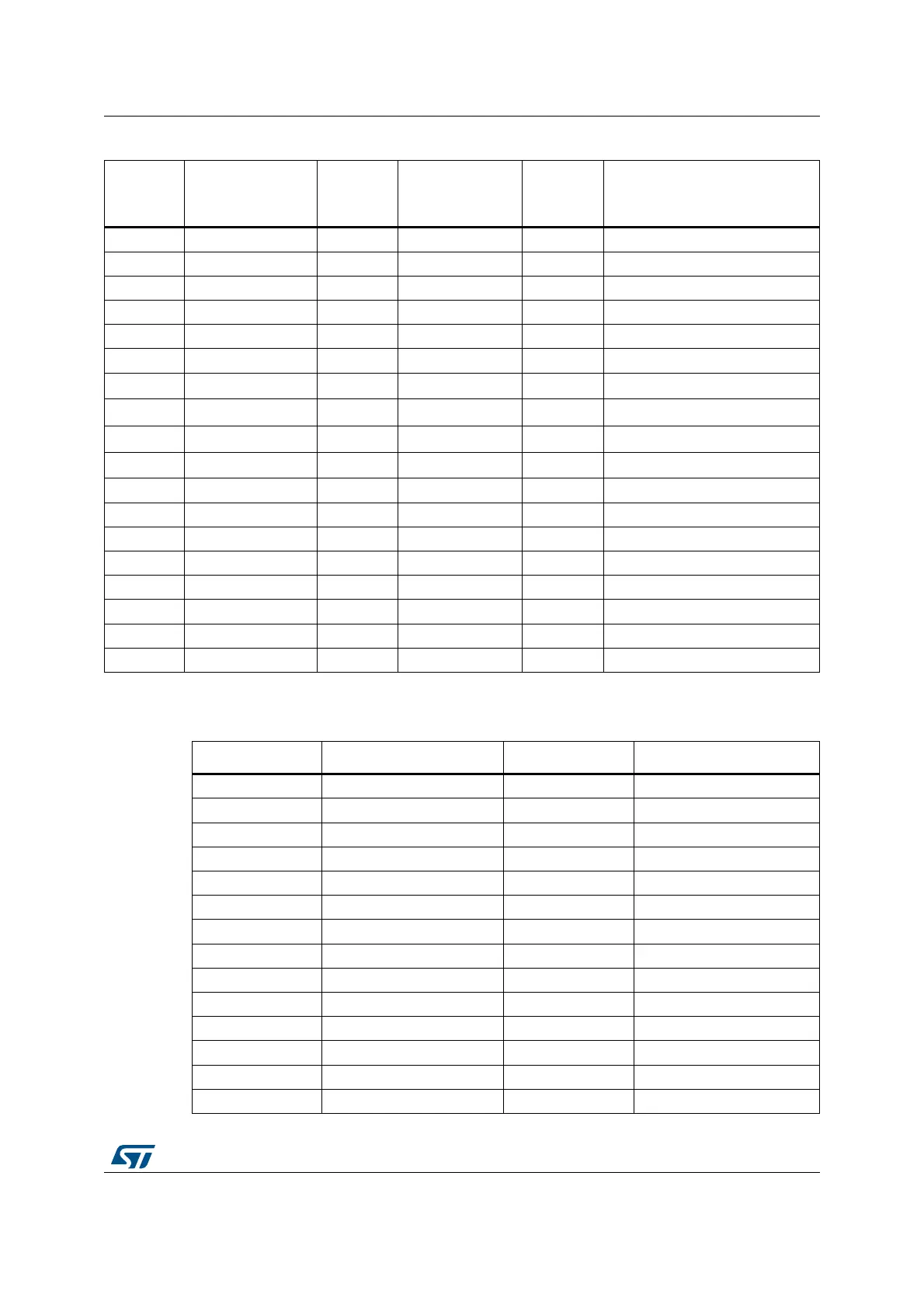

Table 92. DMAMUX: assignment of trigger inputs to resources

Trigger input Resource Trigger input Resource

0 EXTI LINE0 16 DMAMUX1_ch0_event

1 EXTI LINE1 17 DMAMUX1_ch1_event

2 EXTI LINE2 18 DMAMUX1_ch2_event

3 EXTI LINE3 19 DMAMUX1_ch3_event

4 EXTI LINE4 20 LPTIM1_OUT

5 EXTI LINE5 21 Reserved

6 EXTI LINE6 22 Reserved

7 EXTI LINE7 23 Reserved

8 EXTI LINE8 24 Reserved

9 EXTI LINE9 25 Reserved

10 EXTI LINE10 26 Reserved

11 EXTI LINE11 27 Reserved

12 EXTI LINE12 28 Reserved

13 EXTI LINE13 29 Reserved

Loading...

Loading...