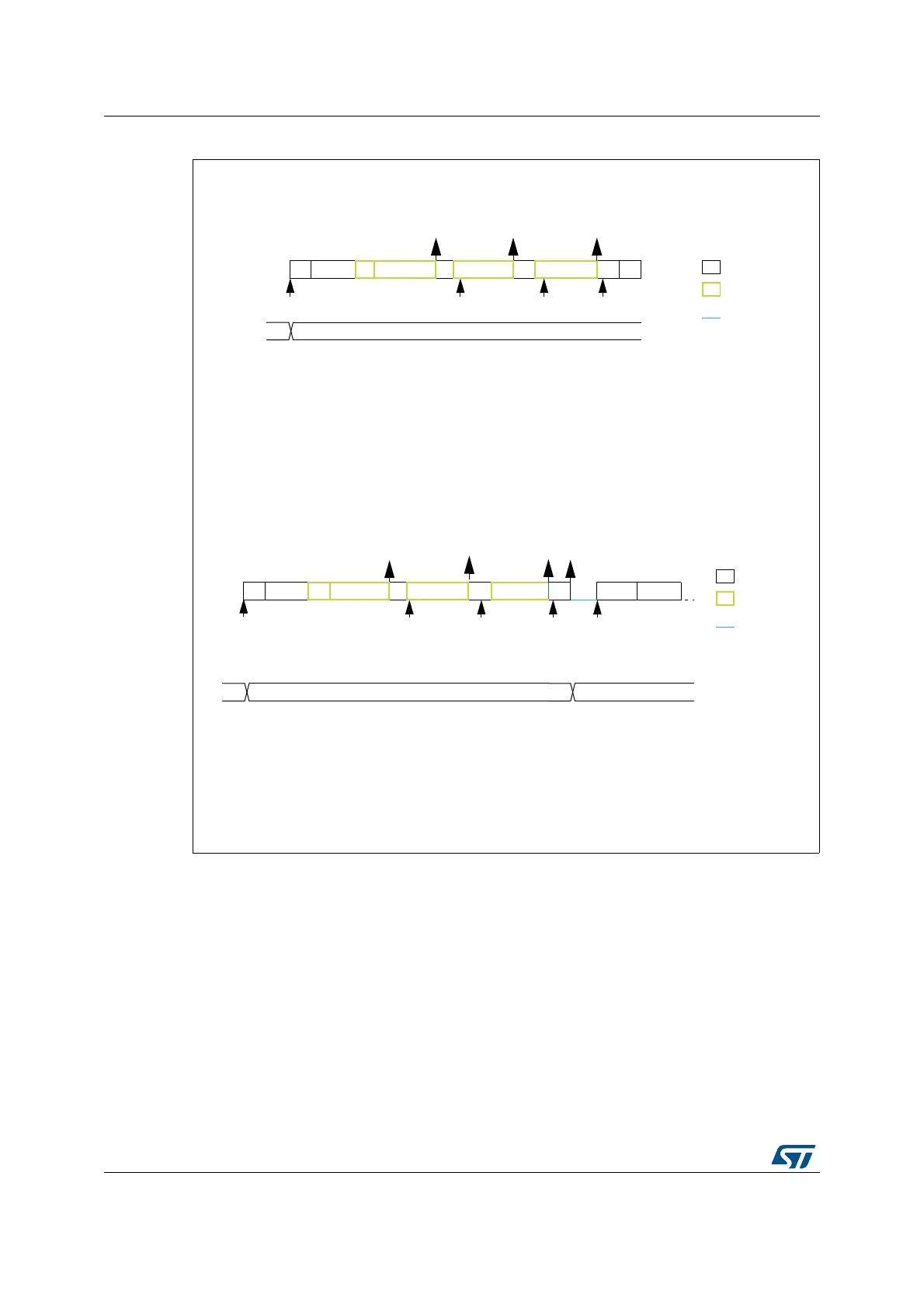

Figure 658. Bus transfer diagrams for SMBus master receiver

MS19872V2

Example SMBus master receiver 2 bytes + PEC, automatic end mode (STOP)

Address

S

INIT: program Slave address, program NBYTES = 3, AUTOEND=1, set PECBYTE, set START

EV1: RXNE ISR: rd data1

EV2: RXNE ISR: rd data2

EV3: RXNE ISR: rd PEC

A

data1

A

RXNE RXNE

data2

A

NBYTES

NA

legend:

transmission

reception

SCL stretch

3VE1VE

xx 3

INIT

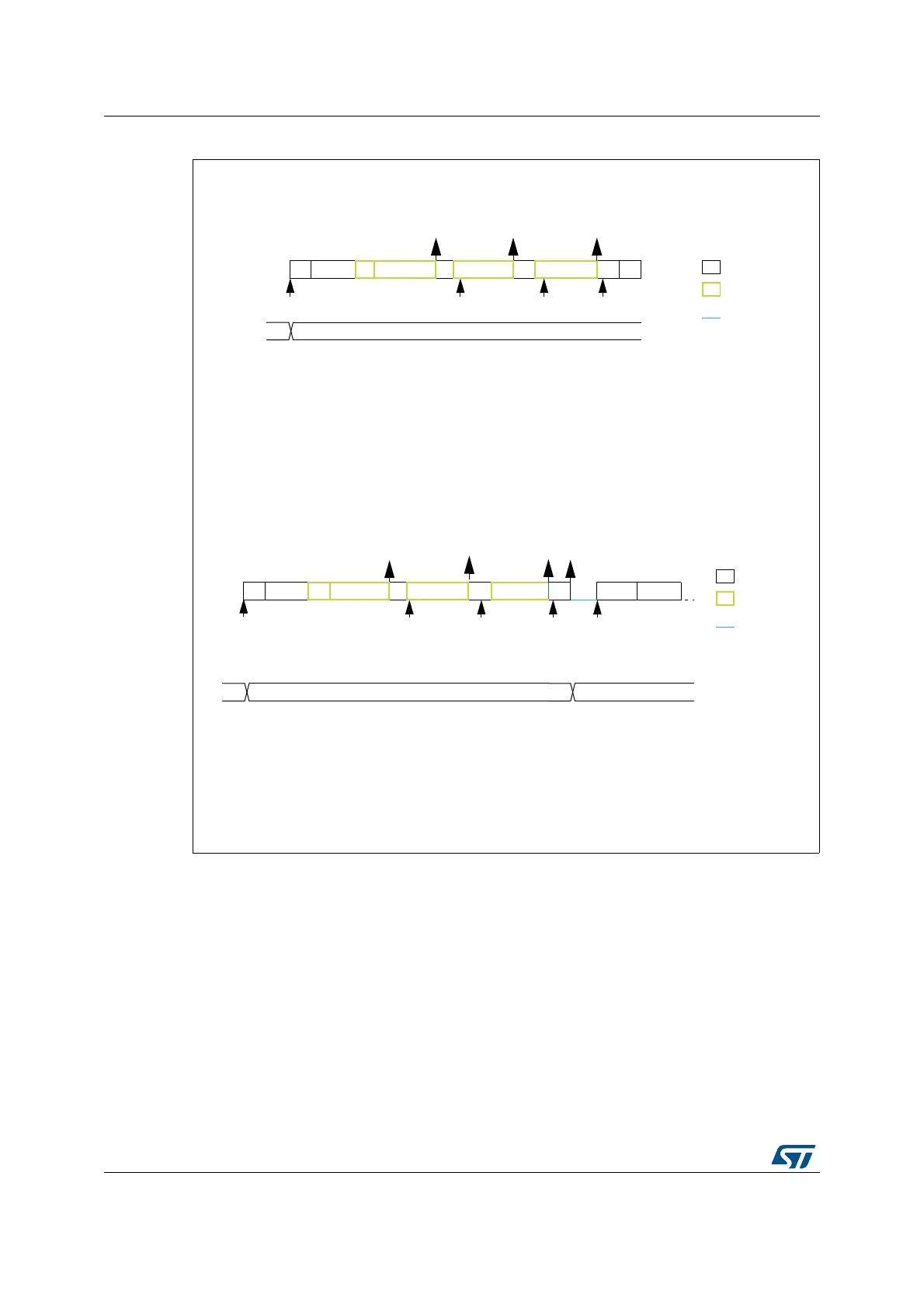

Example SMBus master receiver 2 bytes + PEC, software end mode (RESTART)

Address

S

INIT: program Slave address, program NBYTES = 3, AUTOEND=0, set PECBYTE, set START

EV1: RXNE ISR: rd data1

EV2: RXNE ISR: rd data2

EV3: RXNE ISR: read PEC

EV4: TC ISR: program Slave address, program NBYTES = N, set START

A

data1

A

RXNE RXNE

data2

A

NBYTES

Restart

legend:

transmission

reception

SCL stretch

EV1 EV2

xx

INIT

Address

N

PEC

P

RXNE

EV2

NA

PEC

RXNE

3

EV3

TC

EV4

Loading...

Loading...