General-purpose timers (TIM2/TIM3/TIM4/TIM5) RM0440

1278/2126 RM0440 Rev 4

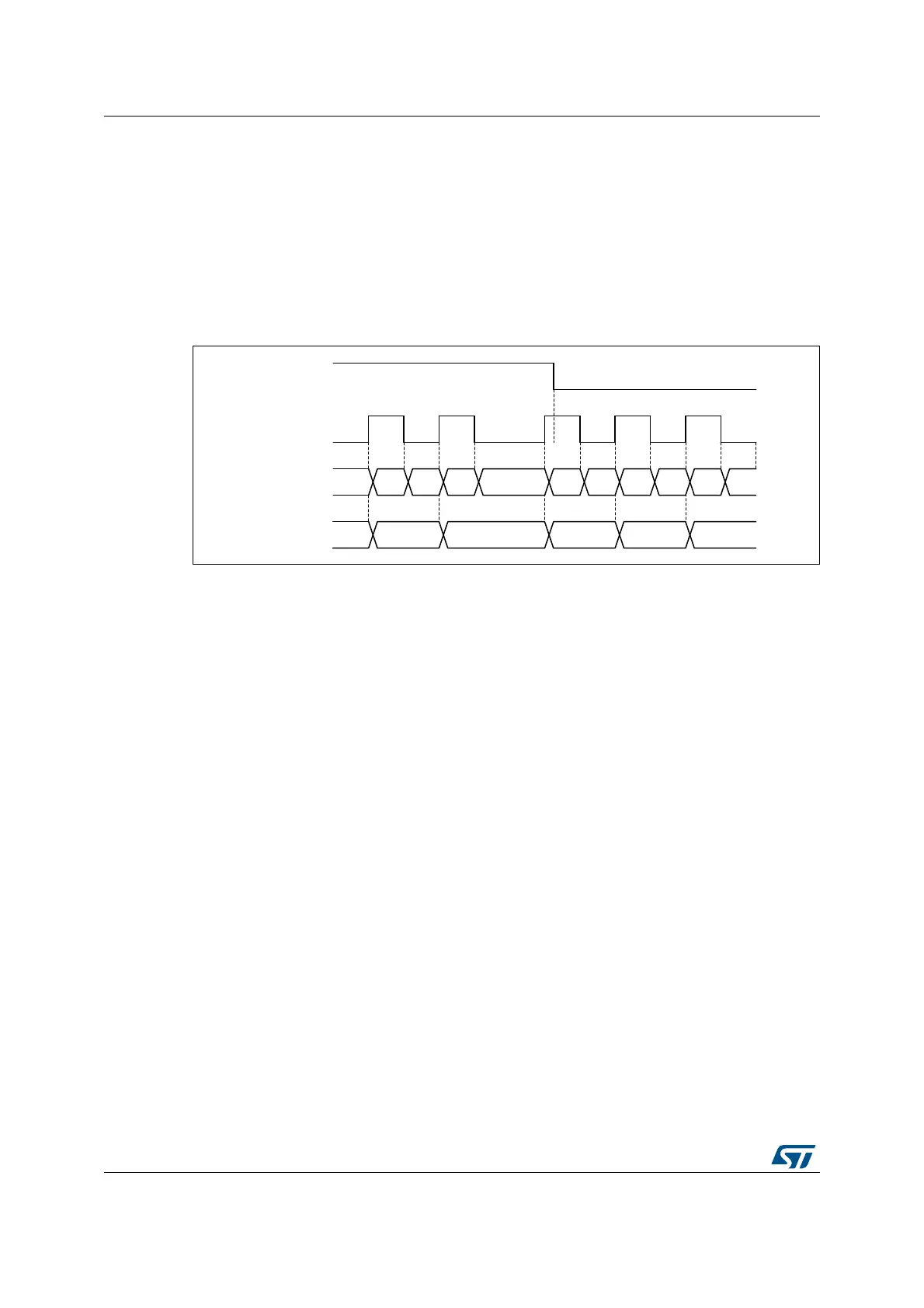

This mode is enabled with the SMS[3:0] bitfield in the TIMx_SMCR register, as following:

• 1010: x2 mode, the counter is updated on both rising and falling edges of the clock

• 1011: x1 mode, the counter is updated on a single clock edge, as per CC2P bit value:

CC2P = 0 corresponds to rising edge sensitivity and CC2P = 1 corresponds to falling

edge sensitivity

The polarity of the direction signal on tim_ti1 is set with the CC1P bit: 0 corresponds to

positive polarity (up-counting when tim_ti1 is high and down-counting when tim_ti1 is low)

and CC1P = 1 corresponds to negative polarity (up-counting when tim_ti1 is low).

Figure 408. Direction plus clock encoder mode

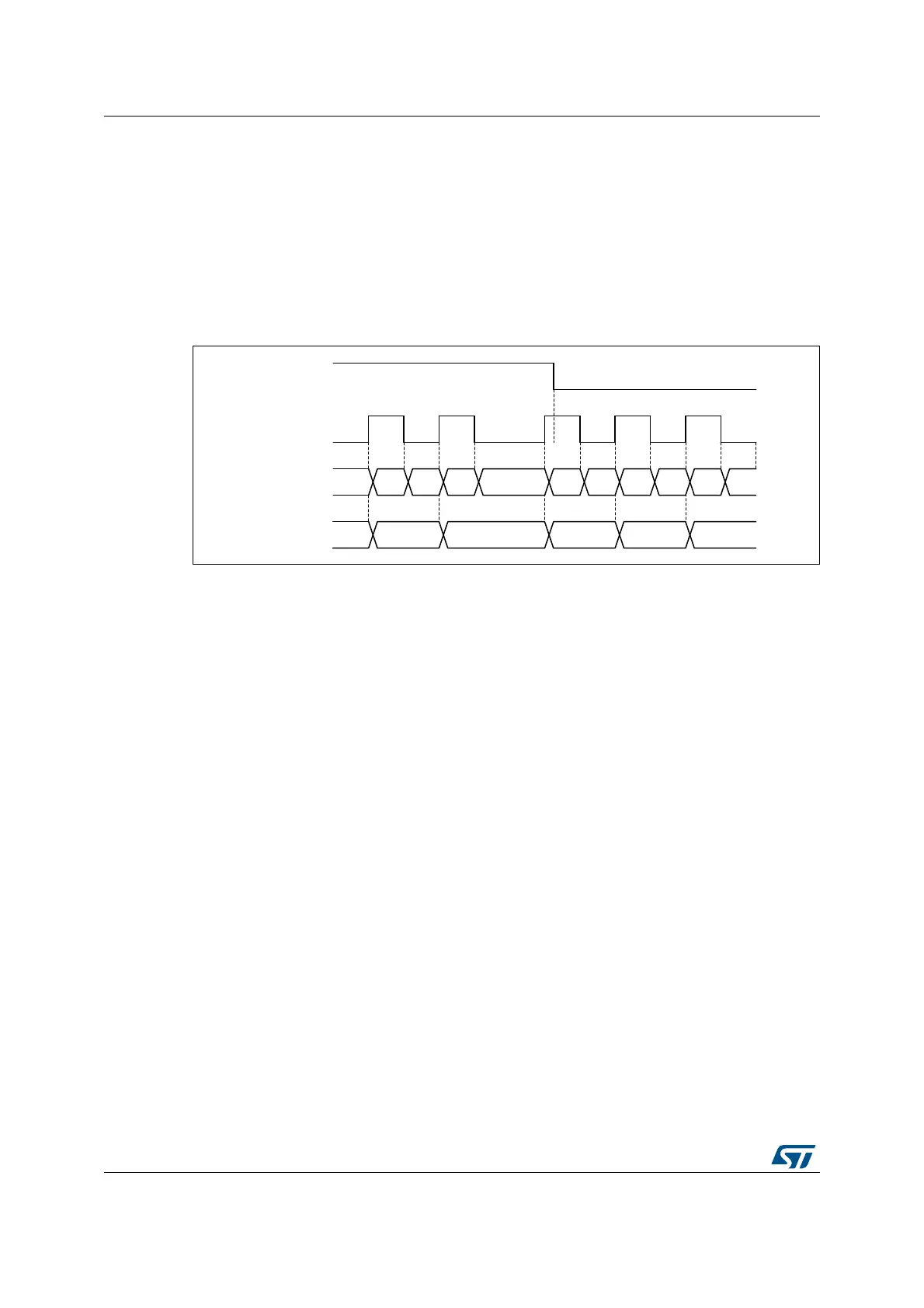

Directional Clock encoder mode

In the “directional clock” mode on Figure 409, the clocks are provided on two lines, with a

single one at once, depending on the direction, so as to have one up-counting clock line and

one down-counting clock line.

This mode is enabled with the SMS[3:0] bitfield in the TIMx_SMCR register, as following:

• 1100: x2 mode, the counter is updated on both rising and falling edges of any of the two

clock line. The CC1P and CC2P bits are coding for the clock idle state. CCxP = 0

corresponds to high-level idle state (refer to Figure 409 below) and CCxP = 1

corresponds to low-level idle state (refer to Figure 410 below).

• 1101: x1 mode, the counter is updated on a single clock edge, as per CC1P and CC2P

bit value. CCxP = 0 corresponds to falling edge sensitivity and high-level idle state

(refer to Figure 409 below), CCxP = 1 corresponds to rising edge sensitivity and low-

level idle state (refer to Figure 410 below).

MSv62352V1

tim_ti1

Counter x2 mode

tim_ti2

Counter x1 mode

7 9 8

7

6 8

68 9 10 11 10 9 8 776

Loading...

Loading...