High-resolution timer (HRTIM) RM0440

948/2126 RM0440 Rev 4

Burst DMA transfers

In addition to the standard DMA requests, the HRTIM features a DMA burst controller to

have multiple registers updated with a single DMA request. This allows to:

• update multiple data registers with one DMA channel only,

• reprogram dynamically one or several timing units, for converters using multiple timer

outputs.

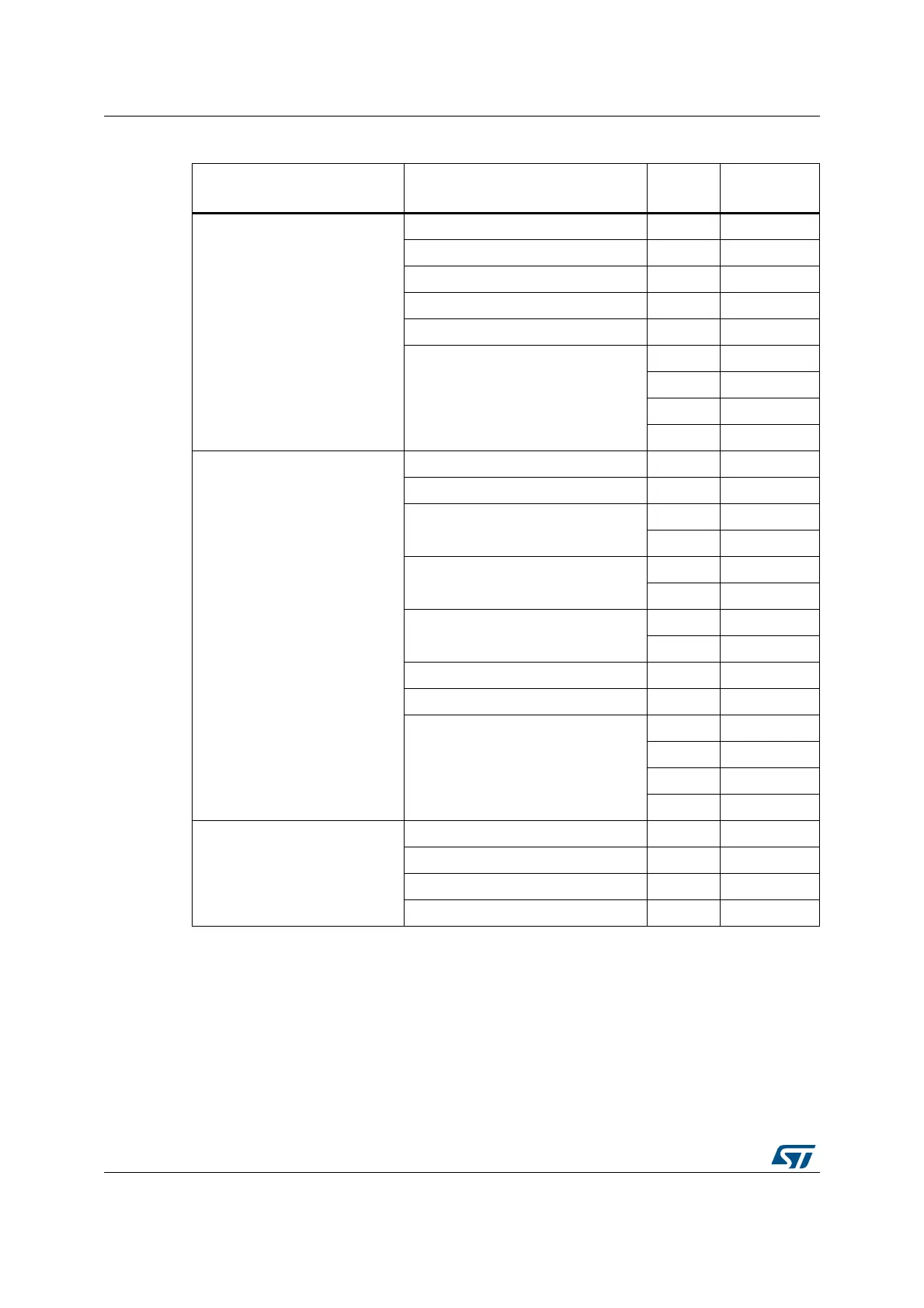

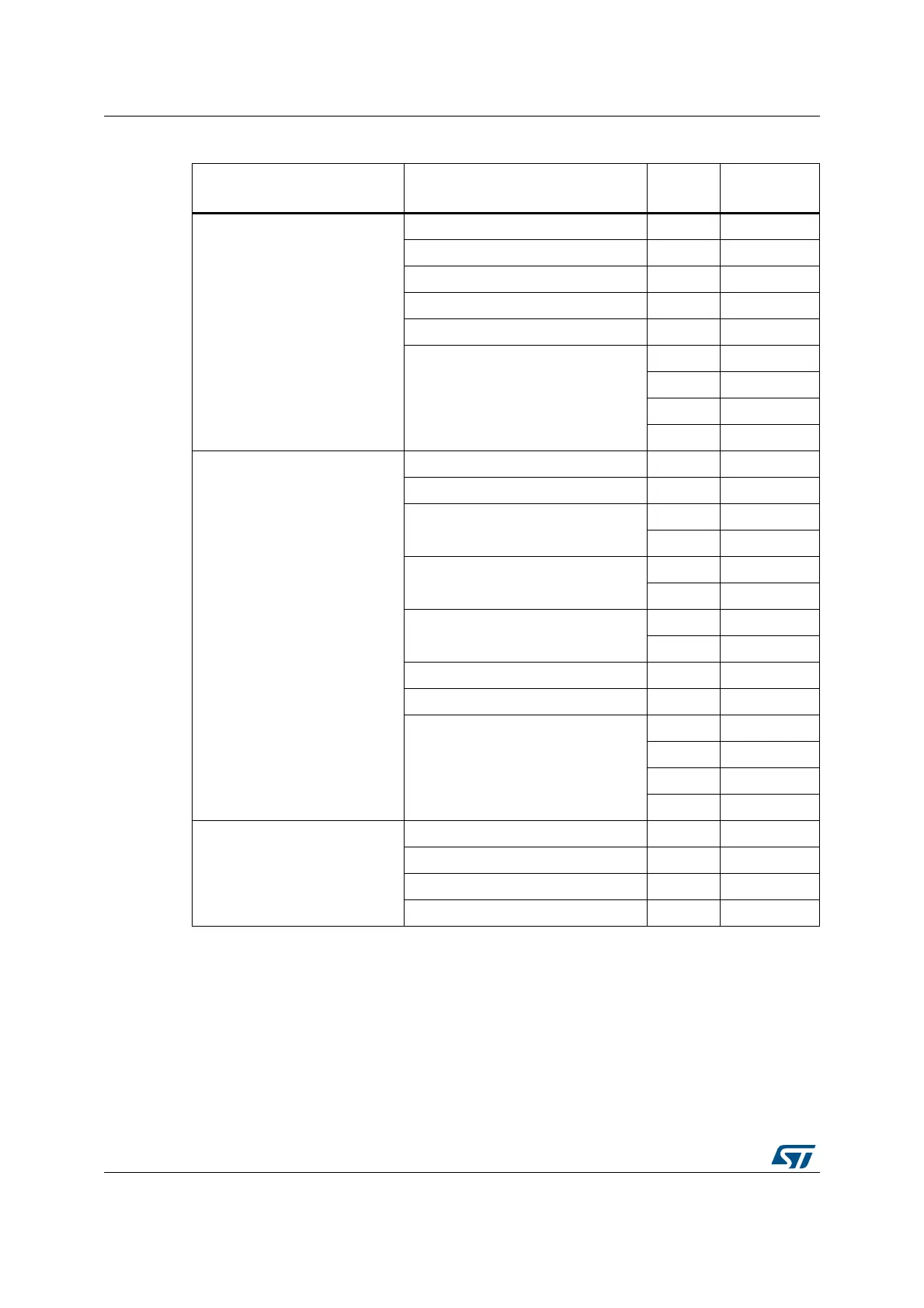

Table 240. HRTIM DMA request summary

DMA Channel Event

DMA

capable

DMA enable

bit

hrtim_dma1

(master timer)

Burst mode period completed No N/A

DLL calibration done No N/A

Master timer registers update Yes MUPDDE

Synchronization event received Yes SYNCDE

Master timer repetition event Yes MREPDE

Master compare 1 to 4 event

Yes MCMP1DE

Yes MCMP2DE

Yes MCMP3DE

Yes MCMP4DE

hrtim_dma2 (timer A)

hrtim_dma3 (timer B)

hrtim_dma4 (timer C)

hrtim_dma5 (timer D)

hrtim_dma6 (timer E)

hrtim_dma7 (timer F)

Delayed protection triggered Yes DLYPRTDE

Counter reset or roll-over event Yes RSTDE

Output 1 and output 2 reset (transition

active to inactive)

Yes RSTx1DE

Yes RSTx2DE

Output 1 and output 2 set (transition

inactive to active)

Yes SET x1DE

Yes SET x2DE

Capture 1 and 2 events

Yes CPT1 DE

Yes CPT2 DE

Timing unit registers update Yes UPDDE

Repetition event Yes REPDE

Compare 1 to 4 event

Yes CMP1D E

Yes CMP2D E

Yes CMP3D E

Yes CMP4D E

N/A

System fault No N/A

Fault 1 to 6 No N/A

Burst mode period completed No N/A

DLL calibration done No N/A

Loading...

Loading...