Peripherals interconnect matrix RM0440

400/2126 RM0440 Rev 4

Active power mode

Run, Sleep, Low-power run, Low-power sleep.

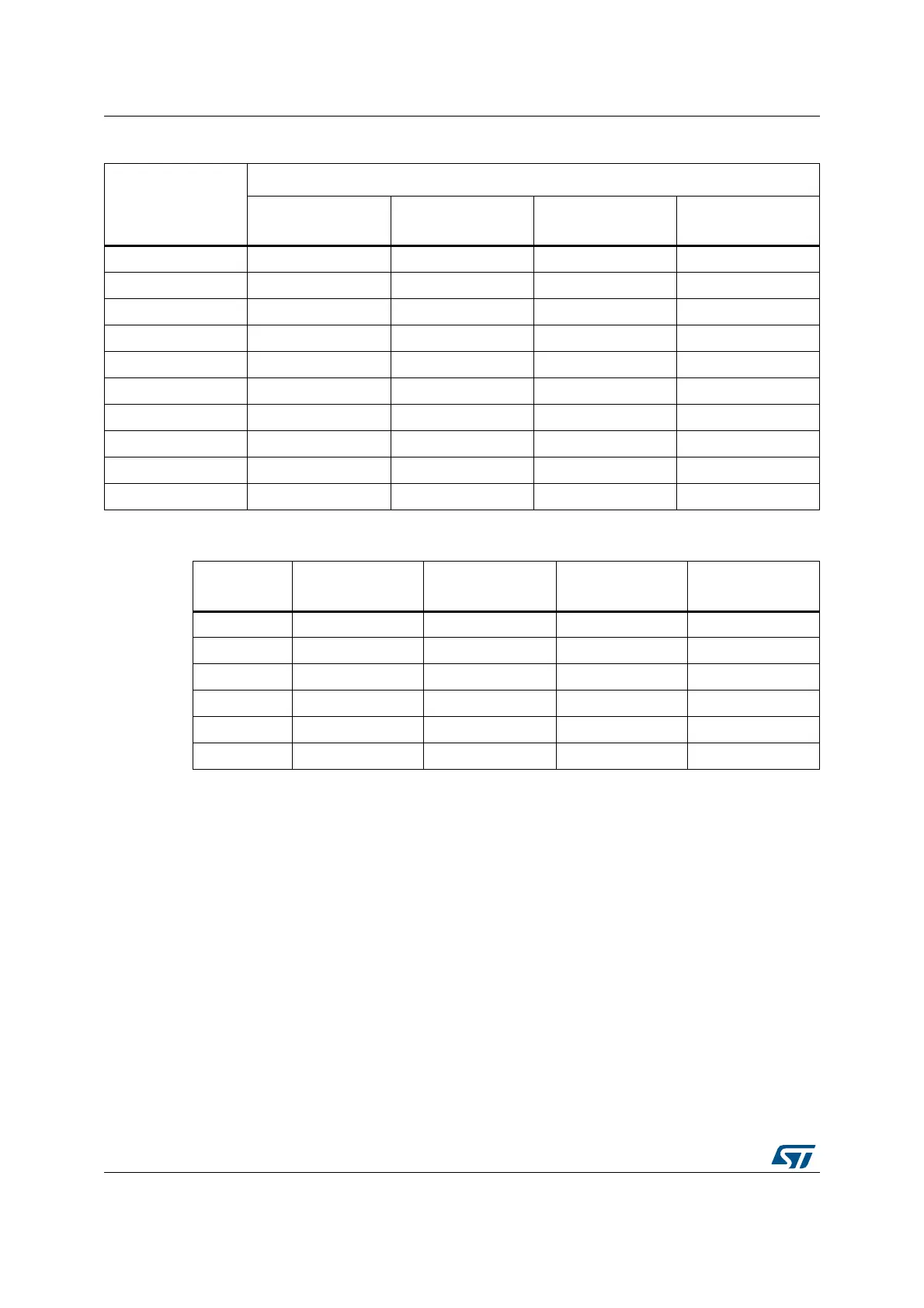

Table 81. Interconnect 10

HRTIM external

event input signal

HRTIM external event signal assignment

EExSRC[1:0]=0

(from GPIO pin)

EExSRC[1:0]=1 EExSRC[1:0]=2 EExSRC[1:0]=3

hrtim_eev1[4:1] HRTIM_EEV1 comp2_out tim1_trgo adc1_AWD1

hrtim_eev2[4:1] HRTIM_EEV2 comp4_out tim2_trgo adc1_AWD2

hrtim_eev3[4:1] HRTIM_EEV3 comp6_out tim3_trgo adc1_AWD3

hrtim_eev4[4:1] HRTIM_EEV4 comp1_out comp5_out adc2_AWD1

hrtim_eev5[4:1] HRTIM_EEV5 comp3_out comp7_out adc2_AWD2

hrtim_eev6[4:1] HRTIM_EEV6 comp2_out comp1_out adc2_AWD3

hrtim_eev7[4:1] HRTIM_EEV7 comp4_out tim7_trgo adc3_AWD1

hrtim_eev8[4:1] HRTIM_EEV8 comp6_out comp3_out adc4_AWD1

hrtim_eev9[4:1] HRTIM_EEV9 comp5_out tim15_trgo comp4_out

hrtim_eev10[4:1] HRTIM_EEV10 comp7_out tim6_trgo adc5_AWD1

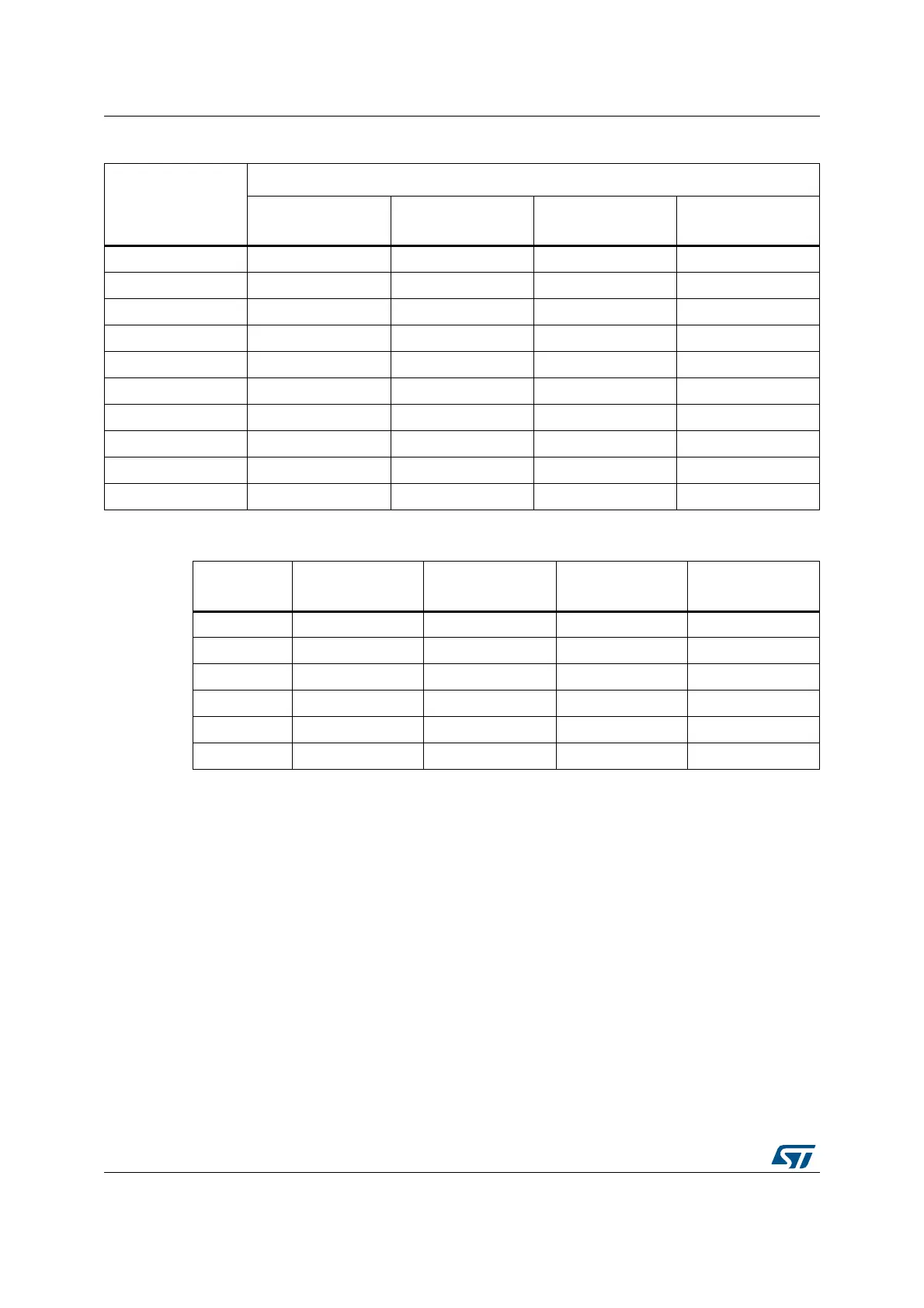

Table 82. Interconnect 11

Fault channel

External Input

FLTxSRC[1:0] = 00

On-chip source

FLTxSRC[1:0] = 01

External Input

FLTxSRC[1:0] = 10

On-chip source

FLTxSRC[1:0] = 11

hrtim_flt1[4:1] HRTIM_FLT1 comp2_out EEV1_muxout N/A

hrtim_flt2[4:1] HRTIM_FLT2 comp4_out EEV2_muxout N/A

hrtim_flt3[4:1] HRTIM_FLT3 comp6_out EEV3_muxout N/A

hrtim_flt4[4:1] HRTIM_FLT4 comp1_out EEV4_muxout N/A

hrtim_flt5[4:1] HRTIM_FLT5 comp3_out EEV5_muxout N/A

hrtim_flt6[4:1] HRTIM_FLT6 comp5_out EEV6_muxout N/A

Loading...

Loading...