Power control (PWR) RM0440

250/2126 RM0440 Rev 4

6.3.8 Standby mode

The Standby mode allows to achieve the lowest power consumption with BOR. It is based

on the Cortex

®

-M4 with FPU deepsleep mode, with the voltage regulators disabled (except

when SRAM2 content is preserved). The PLL, the HSI16, and the HSE oscillators are also

switched off.

SRAM1 and register contents are lost except for registers in the Backup domain and

Standby circuitry (see Figure 12). SRAM2 content can be preserved if the bit RRS is set in

the PWR_CR3 register. In this case the Low-power regulator is ON and provides the supply

to SRAM2 only.

The BOR is always available in Standby mode. The consumption is increased when

thresholds higher than V

BOR0

are used.

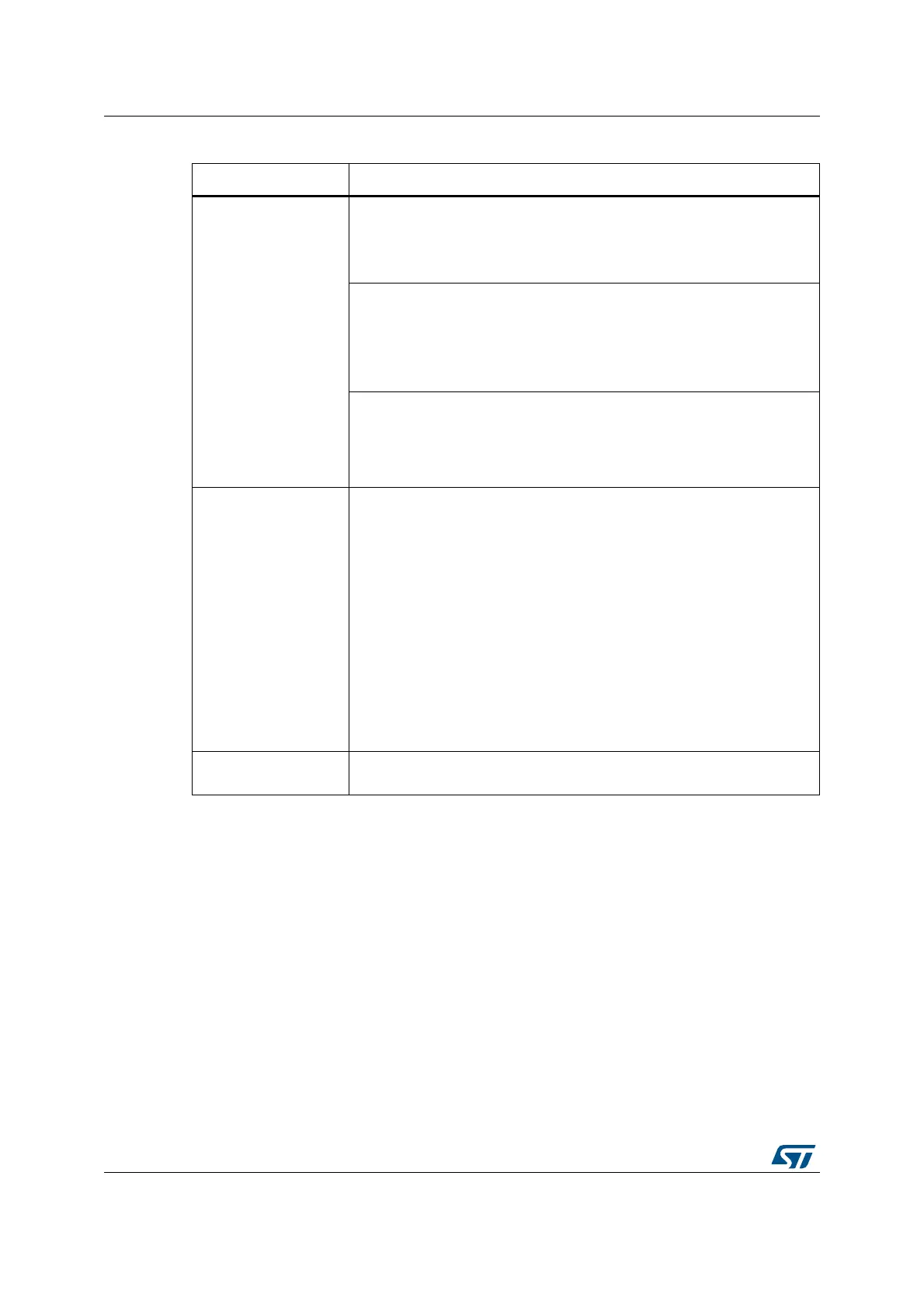

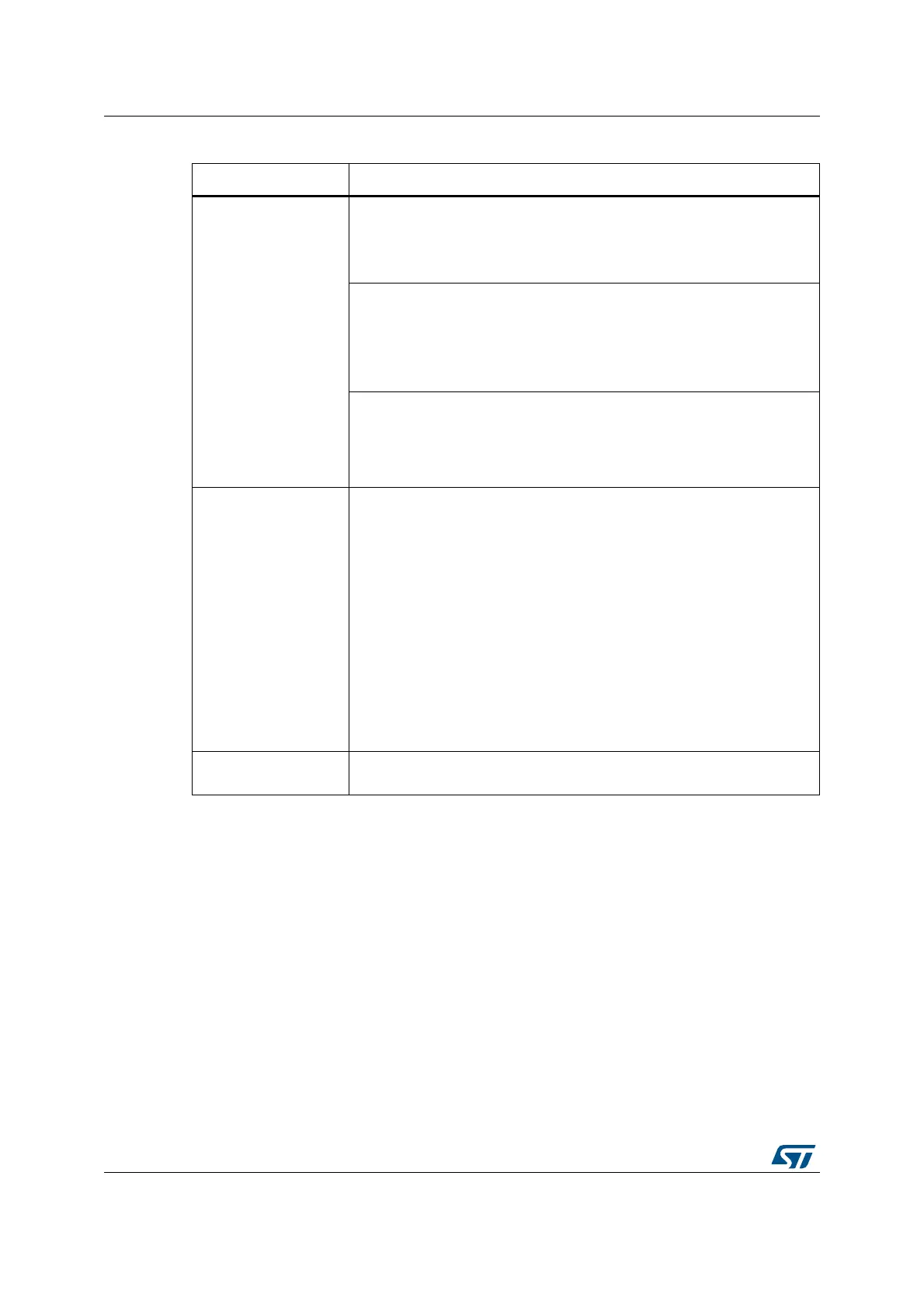

Table 46. Stop 1 mode

Stop 1 mode Description

Mode entry

WFI (Wait for Interrupt) or WFE (Wait for Event) while:

– SLEEPDEEP bit is set in Cortex

®

-M4 with FPU System Control register

– No interrupt (for WFI) or event (for WFE) is pending

– LPMS = “001” in PWR_CR1

On Return from ISR while:

– SLEEPDEEP bit is set in Cortex

®

-M4 with FPU System Control register

– SLEEPONEXIT = 1

– No interrupt is pending

– LPMS = “001” in PWR_CR1

Note: To enter Stop 1 mode, all EXTI Line pending bits (in Section 15.5.6:

Pending register 1 (EXTI_PR1)), and the peripheral flags

generating wakeup interrupts must be cleared. Otherwise, the Stop

1 mode entry procedure is ignored and program execution

continues.

Mode exit

If WFI or Return from ISR was used for entry

Any EXTI Line configured in Interrupt mode (the corresponding EXTI

Interrupt vector must be enabled in the NVIC). The interrupt source can

be external interrupts or peripherals with wakeup capability. Refer to

Table 97: STM32G4 Series vector table.

If WFE was used for entry and SEVONPEND = 0:

Any EXTI Line configured in event mode. Refer to Section 15.3.2:

Wakeup event management.

If WFE was used for entry and SEVONPEND = 1:

Any EXTI Line configured in Interrupt mode (even if the corresponding

EXTI Interrupt vector is disabled in the NVIC). The interrupt source can

be external interrupts or peripherals with wakeup capability. Refer

toTable 97: STM32G4 Series vector table.

Wakeup event: refer to Section 15.3.2: Wakeup event management

Wakeup latency

Longest wakeup time between: HSI16 wakeup time and regulator wakeup

time from Low-power mode + Flash wakeup time from Stop 1 mode.

Loading...

Loading...