Debug support (DBG) RM0440

2082/2126 RM0440 Rev 4

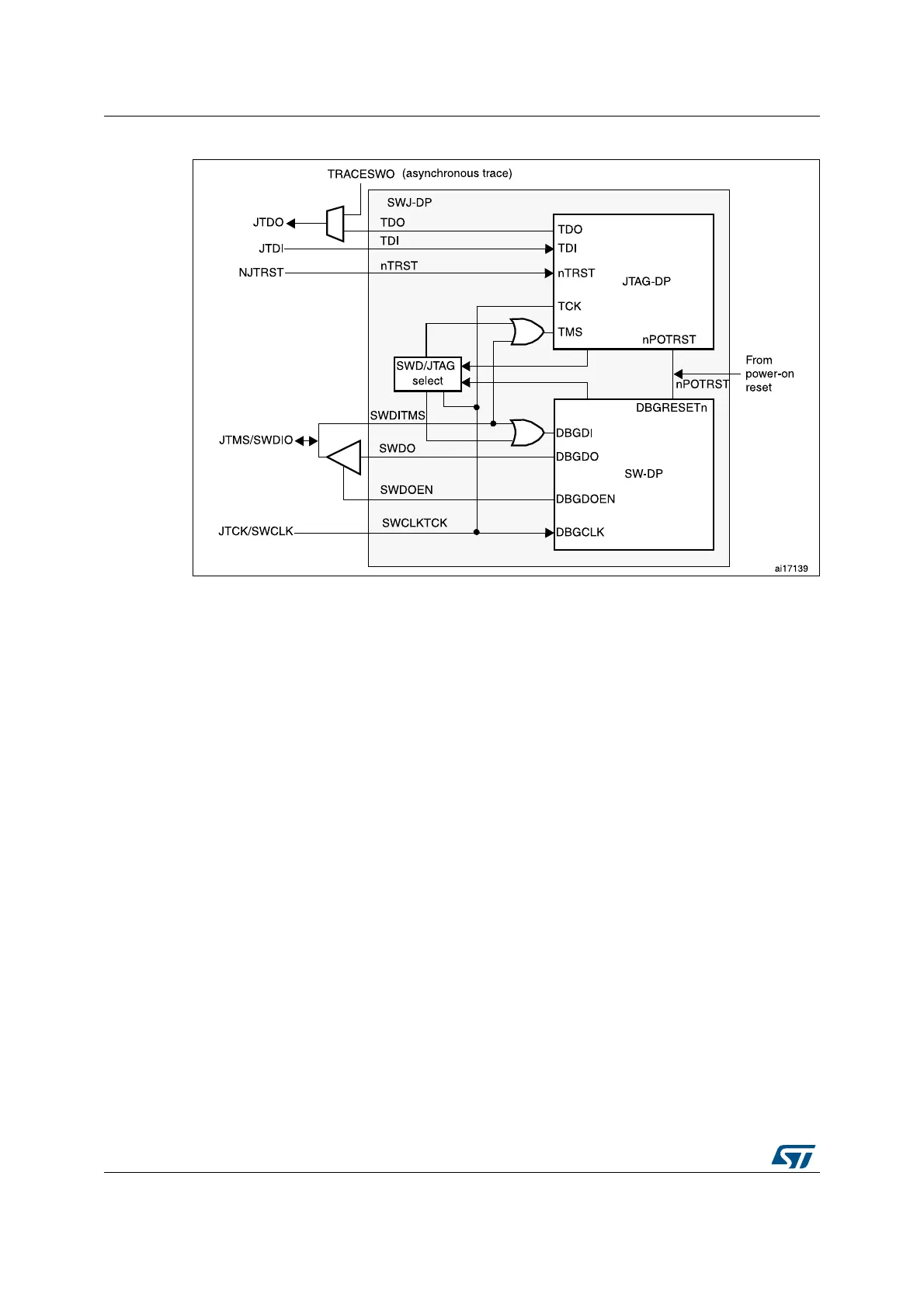

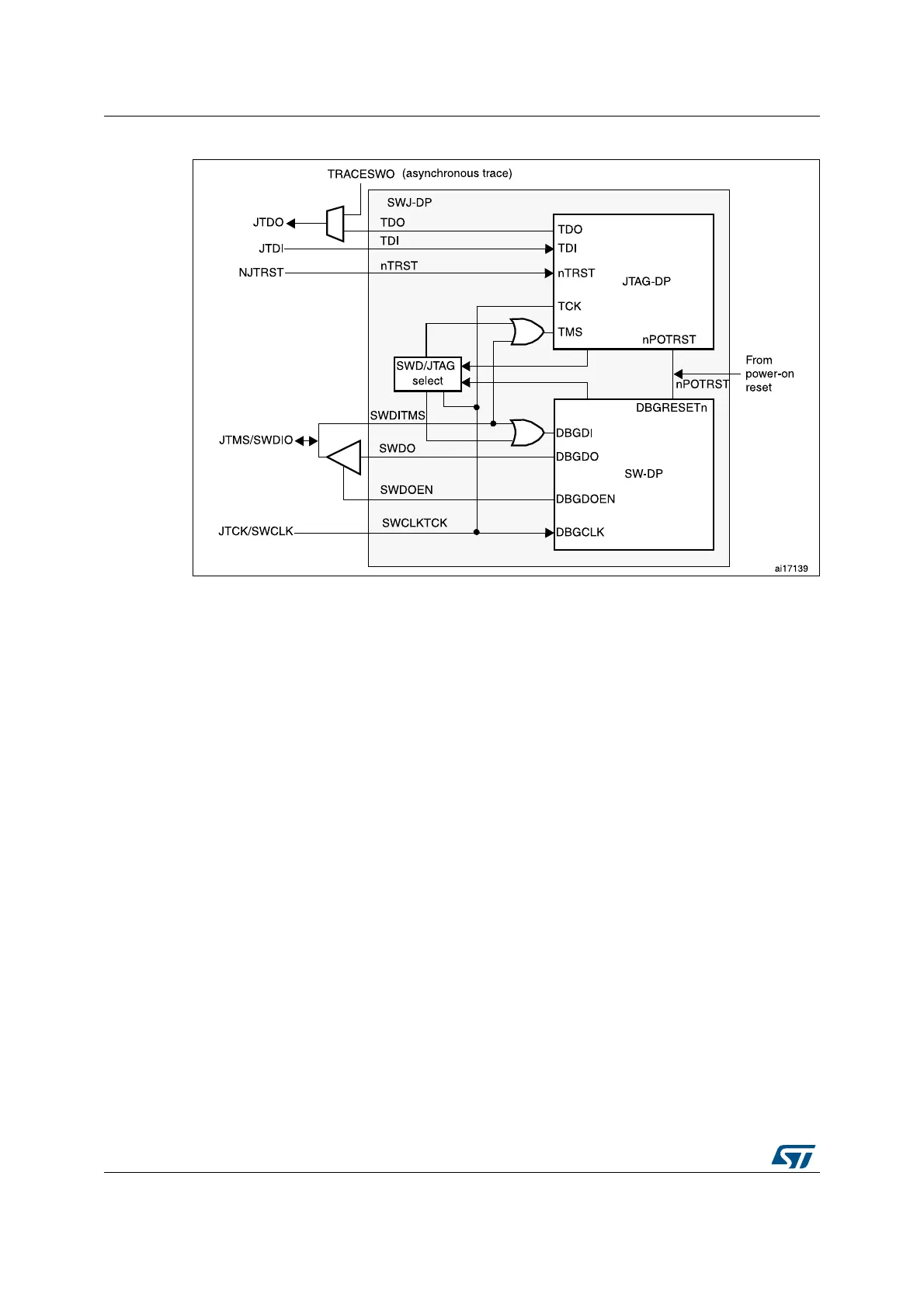

Figure 685. SWJ debug port

Figure 685 shows that the asynchronous TRACE output (TRACESWO) is multiplexed with

TDO. This means that the asynchronous trace can only be used with SW-DP, not JTAG-DP.

47.3.1 Mechanism to select the JTAG-DP or the SW-DP

By default, the JTAG-Debug Port is active.

If the debugger host wants to switch to the SW-DP, it must provide a dedicated JTAG

sequence on TMS/TCK (respectively mapped to SWDIO and SWCLK) which disables the

JTAG-DP and enables the SW-DP. This way it is possible to activate the SWDP using only

the SWCLK and SWDIO pins.

This sequence is:

1. Send more than 50 TCK cycles with TMS (SWDIO) =1

2. Send the 16-bit sequence on TMS (SWDIO) = 0111100111100111 (MSB transmitted

first)

3. Send more than 50 TCK cycles with TMS (SWDIO) =1

47.4 Pinout and debug port pins

The STM32G4 Series MCUs are available in various packages with different numbers of

available pins. As a result, some functionalities (ETM) related to pin availability may differ

between packages.

Loading...

Loading...