RM0440 Rev 4 859/2126

RM0440 High-resolution timer (HRTIM)

1083

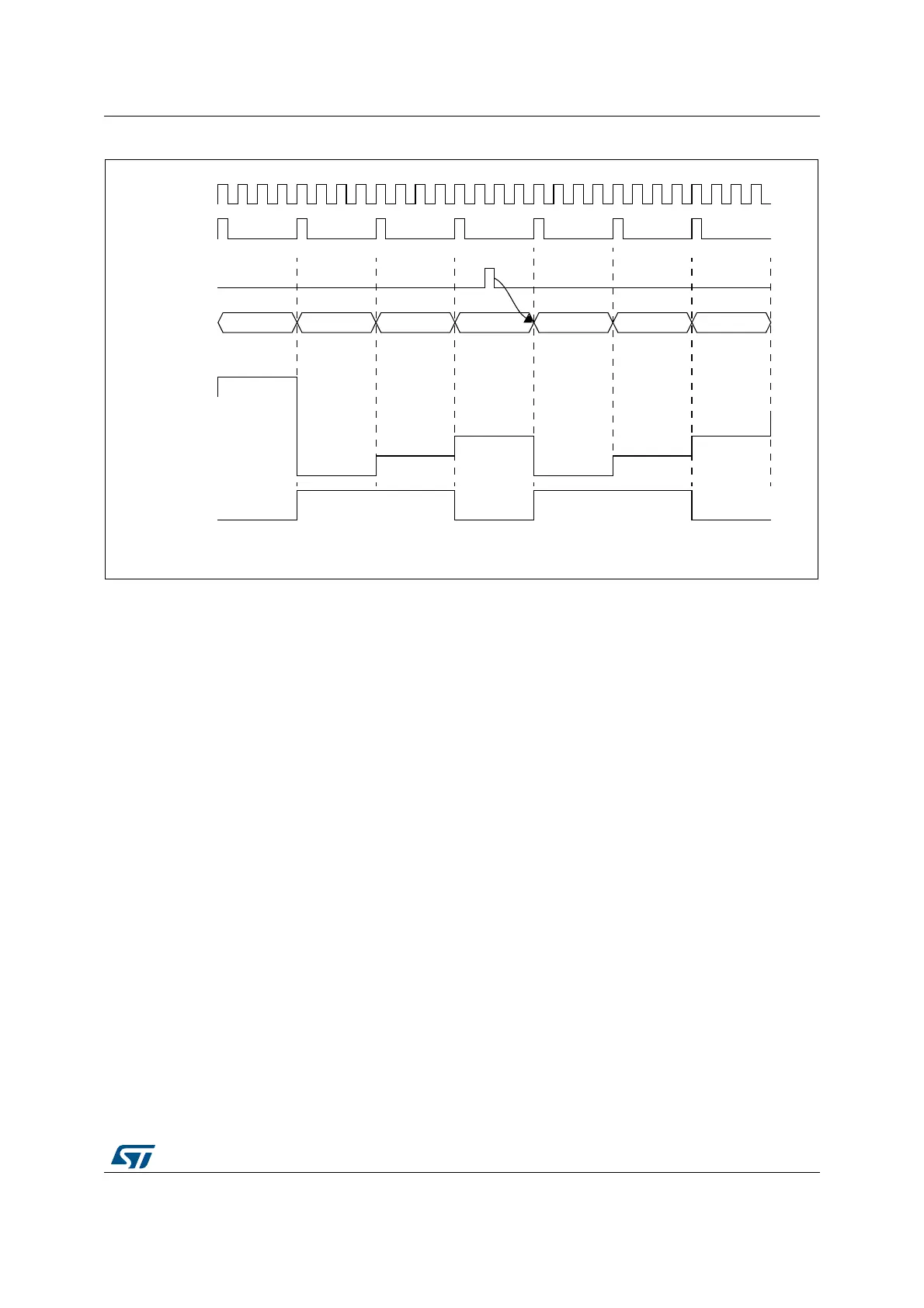

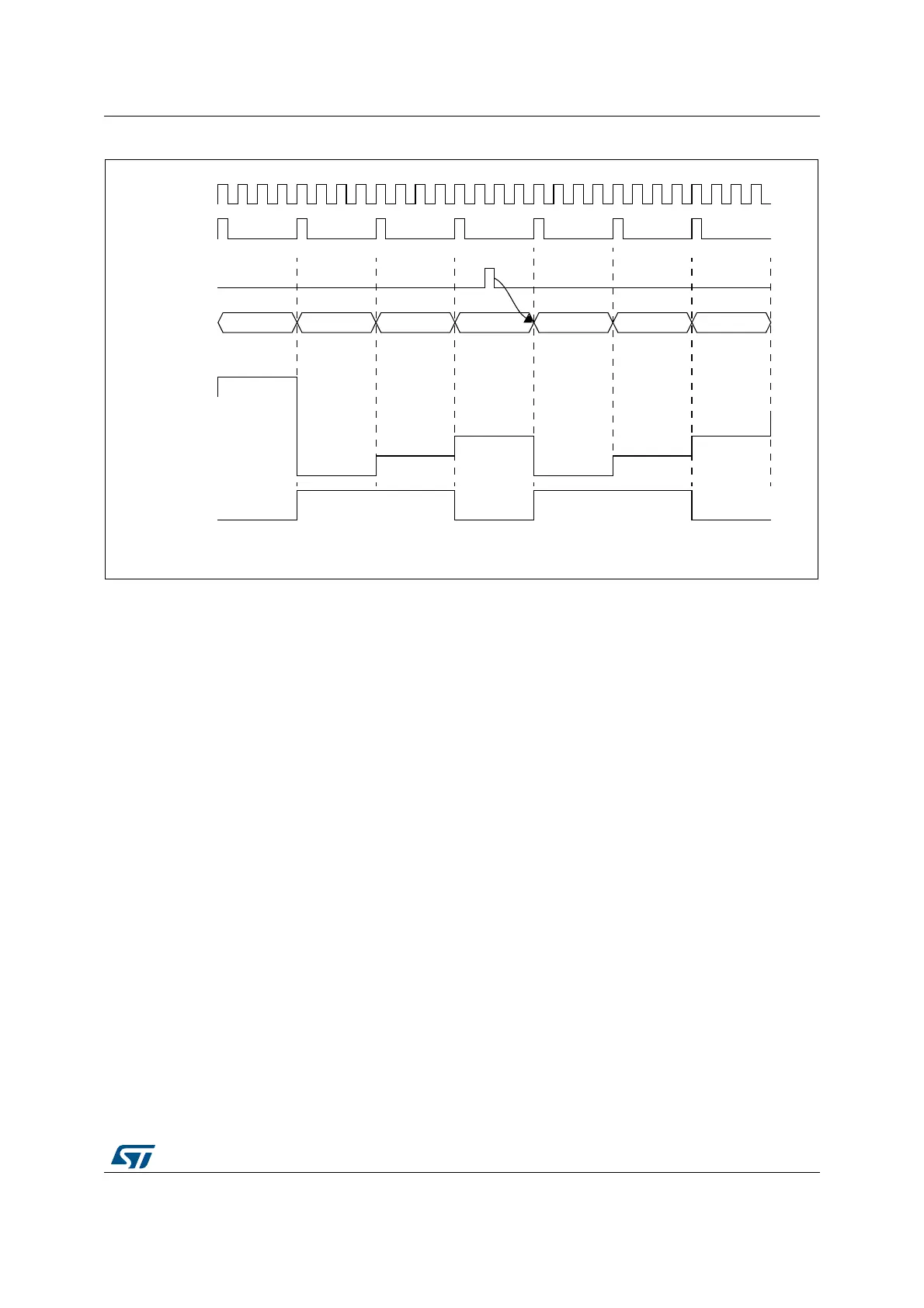

Figure 187. Timer reset resynchronization (prescaling ratio above 32)

Repetition counter

A common software practice is to have an interrupt generated when the period value is

reached, so that the maximum amount of time is left for processing before the next period

begins. The main purpose of the repetition counter is to adjust the period interrupt rate and

off-load the CPU by decoupling the switching frequency and the interrupt frequency.

The timing units have a repetition counter. This counter cannot be read, but solely

programmed with an auto-reload value in the HRTIM_REPxR register.

The repetition counter is initialized with the content of the HRTIM_REPxR register when the

timer is enabled (TXCEN bit set). Once the timer has been enabled, any time the counter is

cleared, either due to a reset event or due to a counter roll-over, the repetition counter is

decreased. When it reaches zero, a REP interrupt or a DMA request is issued if enabled

(REPIE and REPDE bits in the HRTIM_DIER register).

If the HRTIM_REPxR register is set to 0, an interrupt is generated for each and every

period. For any value above 0, a REP interrupt is generated after (HRTIM_REPxR + 1)

periods. Figure 188 presents the repetition counter operation for various values, in

continuous mode.

MS32261V2

5

0

1

1

2

Prescaled clock

Reset event

Counter

Counter

(PER = 5)

f

HRTIM

HRTIM_CHA1

HRTIM_CHA1: Set on Timer A reset event, Reset on Compare 1 = 2

Loading...

Loading...