RM0440 Rev 4 677/2126

RM0440 Analog-to-digital converters (ADC)

724

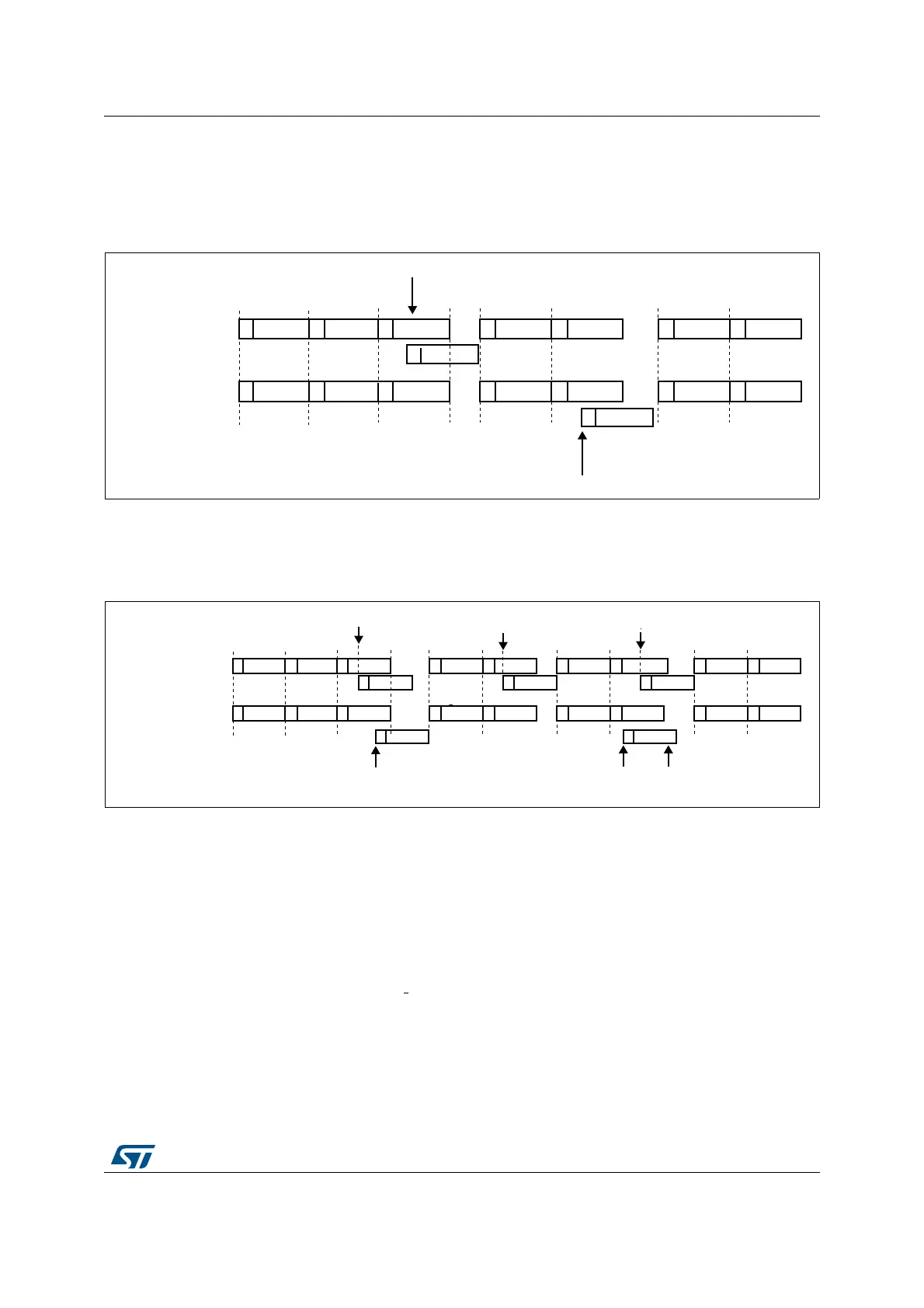

Note: In combined regular simultaneous + alternate trigger mode, one must convert sequences

with the same length or ensure that the interval between triggers is longer than the long

conversion time of the 2 sequences. Otherwise, the ADC with the shortest sequence may

restart while the ADC with the longest sequence is completing the previous conversions.

Figure 145. Alternate + regular simultaneous

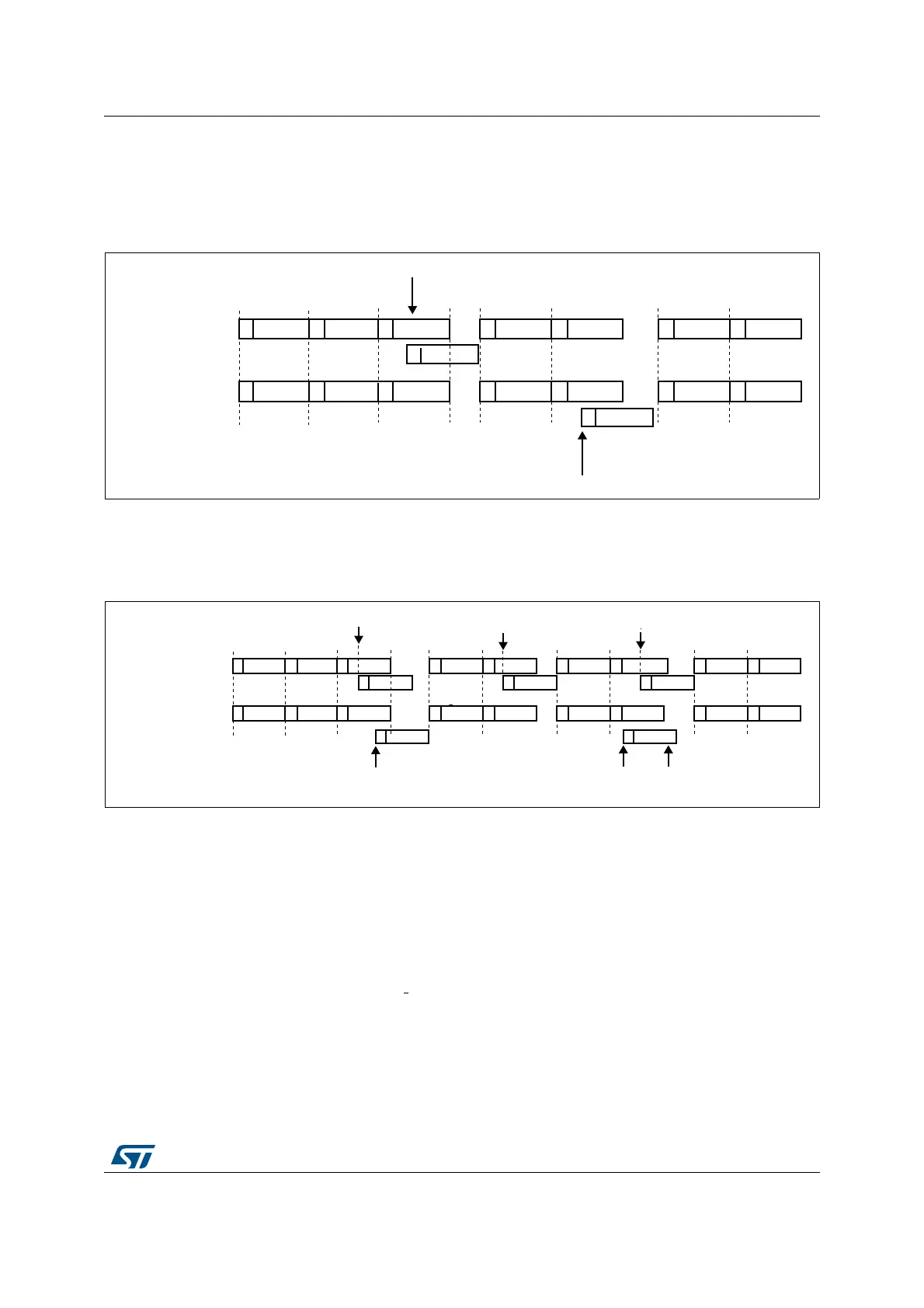

If a trigger occurs during an injected conversion that has interrupted a regular conversion,

the alternate trigger is served. Figure 146 shows the behavior in this case (note that the 6th

trigger is ignored because the associated alternate conversion is not complete).

Figure 146. Case of trigger occurring during injected conversion

Combined injected simultaneous plus interleaved

This mode is selected by programming bits DUAL[4:0]=00011

It is possible to interrupt an interleaved conversion with a simultaneous injected event.

In this case the interleaved conversion is interrupted immediately and the simultaneous

injected conversion starts. At the end of the injected sequence the interleaved conversion is

resumed. When the interleaved regular conversion resumes, the first regular conversion

which is performed is alway the master’s one. Figure 147, Figure 148 and Figure 149 show

the behavior using an example.

Caution: In this mode, it is mandatory to use the Common Data Register to read the regular data with

a single read access. On the contrary, master-slave data coherency is not guaranteed.

ADC MASTER reg

CH1 CH2 CH3

CH1

CH3 CH4

CH1

ADC MASTER inj

ADC SLAVE reg

ADC SLAVE inj

1st trigger

2nd trigger

synchro not lost

CH4 CH6 CH7 CH7 CH8

CH4 CH5

CH8 CH9

ai16062V2-m

ADC MASTER reg

CH1

CH14

CH3

ADC MASTER inj

ADC SLAVE reg

ADC SLAVE inj

1st trigger

2nd trigger

CH7 CH9

CH5

CH10

ai16063V2

CH14

4th trigger

3rd trigger

CH15

CH14

5th trigger

CH15

6th trigger

(ignored)

CH5

CH11

CH6

CH12

CH2 CH3 CH4

CH8 CH9 CH10

CH4

CH11

Loading...

Loading...