RM0440 Rev 4 1753/2126

RM0440 Serial peripheral interface / integrated interchip sound (SPI/I2S)

1791

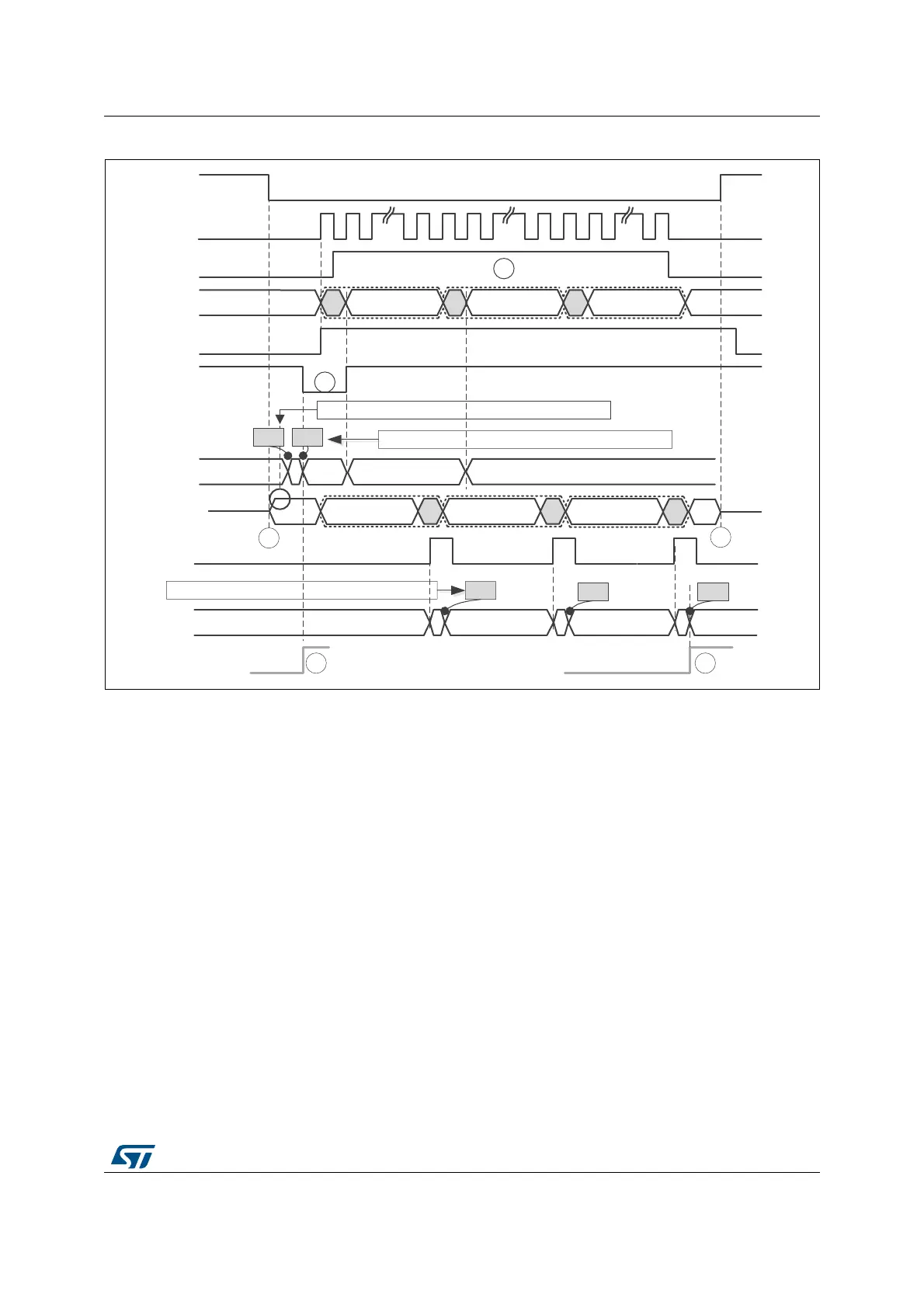

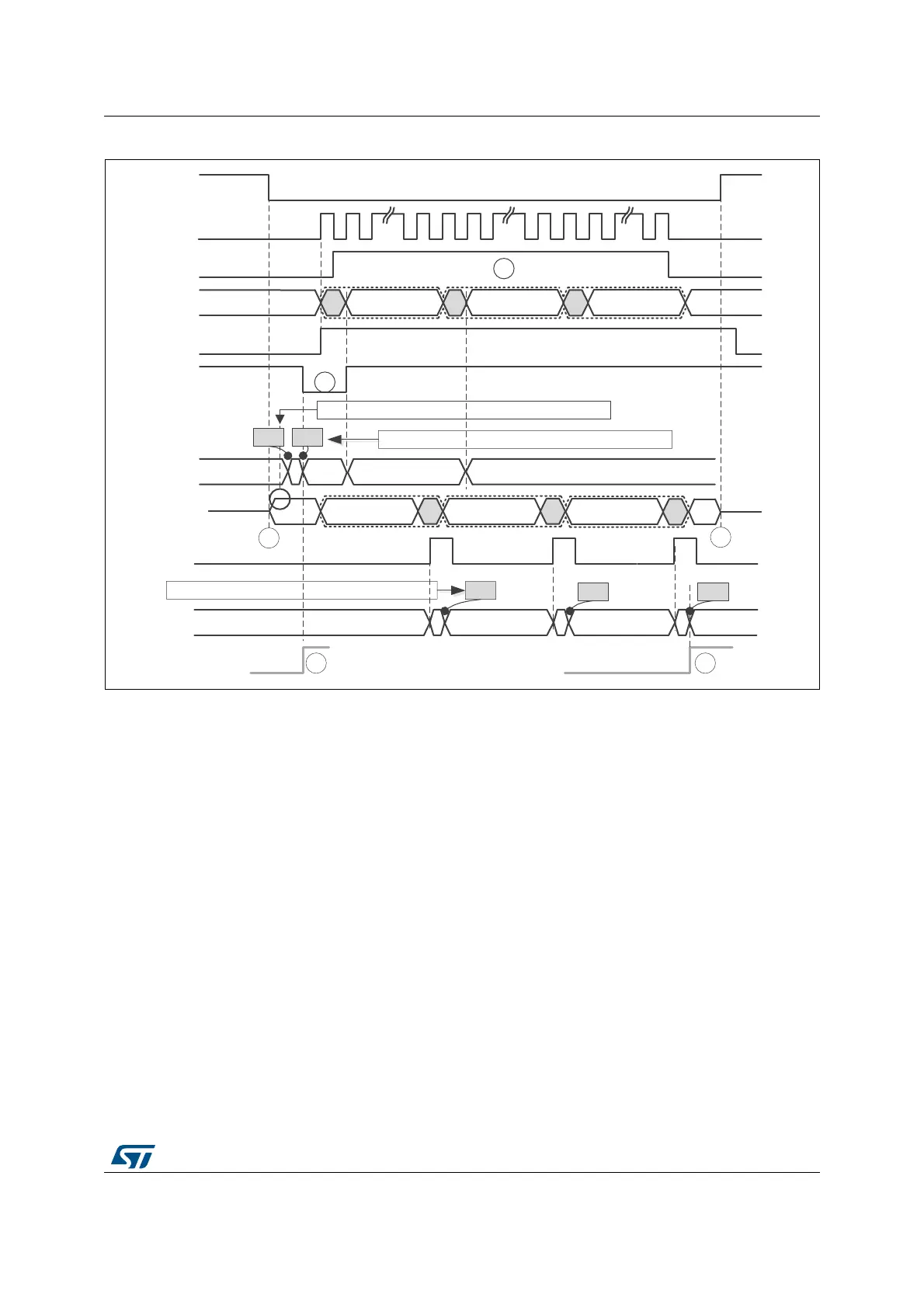

Figure 583. Master full-duplex communication with CRC

Assumptions for master full-duplex communication with CRC example:

• Data size = 16 bit

• CRC enabled

If DMA is used:

• Number of Tx frames transacted by DMA is set to 2

• Number of Rx frames transacted by DMA is set to 3

See also : Communication diagrams on page 1750 for details about common assumptions

and notes.

DTx1

10

DRx1

NSS

SCK

BSY

MOSI

MSB

MSB MSB

DTx2

CRC

SPE

TXE

00

11 10 00

FTLVL

DTx1

DTx2

LSB

DRx2

LSB

CRC

LSB

10

10 0010 0000 00

RXNE

DRx1

DRx2 DRx3

FRLVL

DMA Tx TICF

DMA Rx TICF

1

1

2

3

4

5 6

Enable Tx/Rx DMA or interrupts

DMA or software control at Tx events

DMA or software control at Rx events

MISO

MSv32124V2

Loading...

Loading...