RM0440 Rev 4 739/2126

RM0440 Digital-to-analog converter (DAC)

773

The following conditions must be met to change from Double data to single data mode or

vice versa:

• The DAC must be disabled.

• DMAEN bit must be cleared (ENx=0 and DMAENx=0).

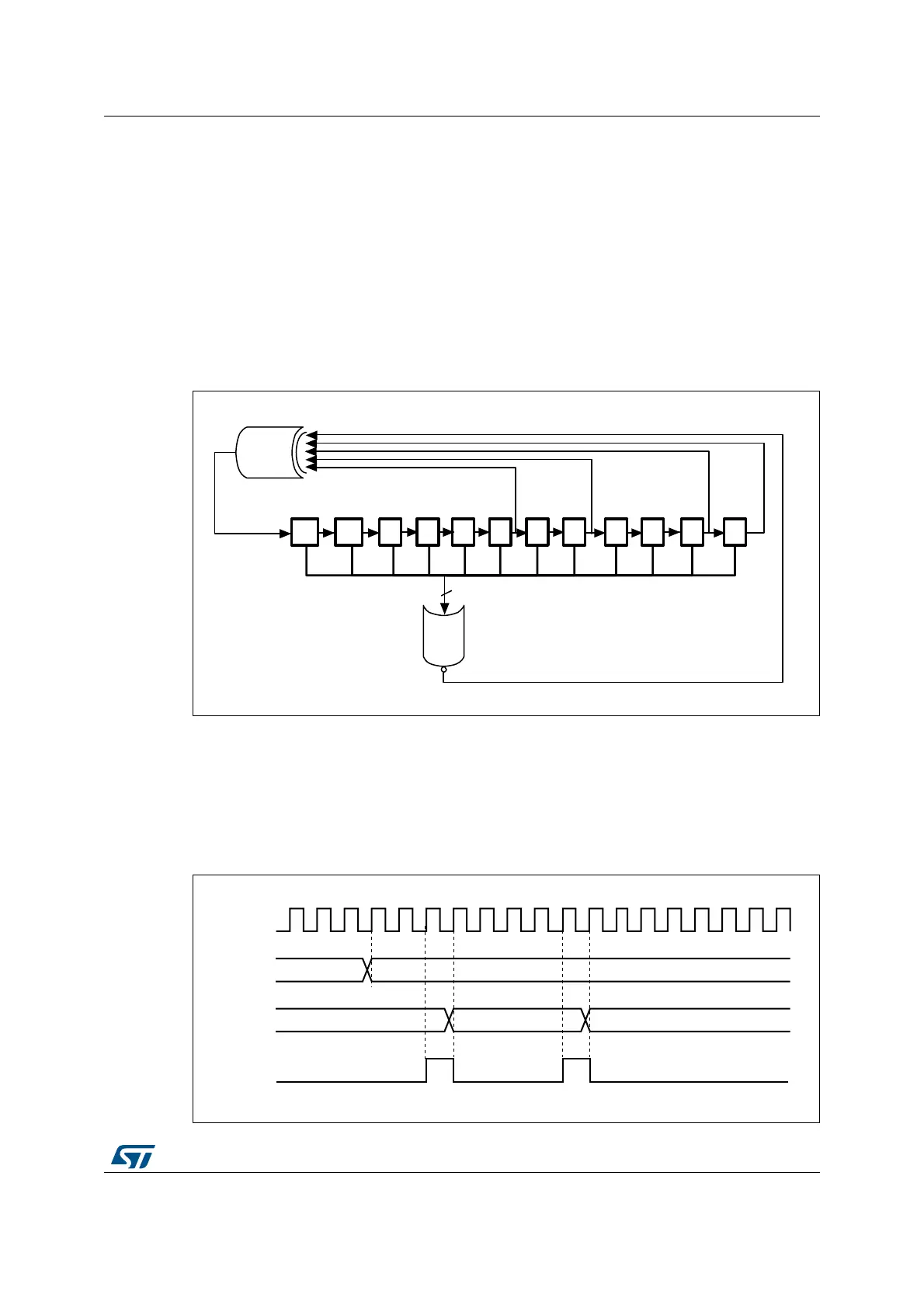

22.4.9 DAC noise generation

In order to generate a variable-amplitude pseudonoise, an LFSR (linear feedback shift

register) is available. DAC noise generation is selected by setting WAVEx[1:0] to 01. The

preloaded value in LFSR is 0xAAA. This register is updated three dac_hclk clock cycles

after each trigger event, following a specific calculation algorithm.

Figure 160. DAC LFSR register calculation algorithm

The LFSR value, that may be masked partially or totally by means of the MAMPx[3:0] bits in

the DAC_CR register, is added up to the DAC_DHRx contents without overflow and this

value is then transferred into the DAC_DORx register.

If LFSR is 0x0000, a ‘1 is injected into it (antilock-up mechanism).

It is possible to reset LFSR wave generation by resetting the WAVEx[1:0] bits.

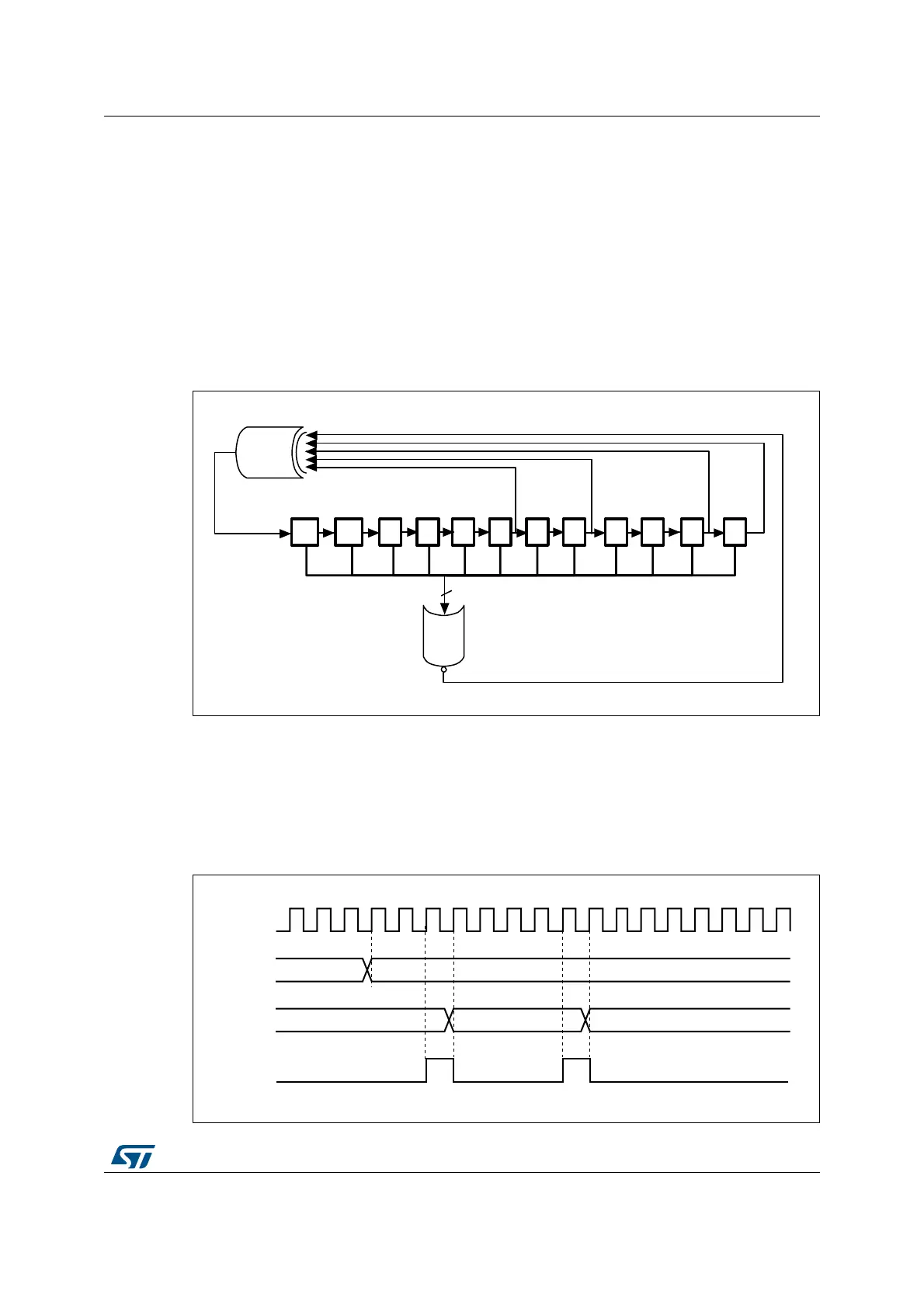

Figure 161. DAC conversion (SW trigger enabled) with LFSR wave generation

11 10 9 8 7 6 5 4 3 2 1 0

12

NOR

X

12

X

0

X

X

4

X

6

XOR

ai14713c

dac_pclk

0x00

0xAAA

DHR

DOR

MS45320V1

0xD55

SWTRIG

Loading...

Loading...