RM0440 Rev 4 913/2126

RM0440 High-resolution timer (HRTIM)

1083

TIMx counter reset causing a TIMx update

Table 229 lists the counter reset sources and indicates whether they can be used to

generate an update.

Operating condition: TxRSTU bit in HRTIM_TIMxCR register.

TIMx update causing a TIMx counter reset

Table 230 lists the update event sources and indicates whether they can be used to

generate a counter reset.

Operating condition: UPDT bit set in HRTIM_RSTxR.

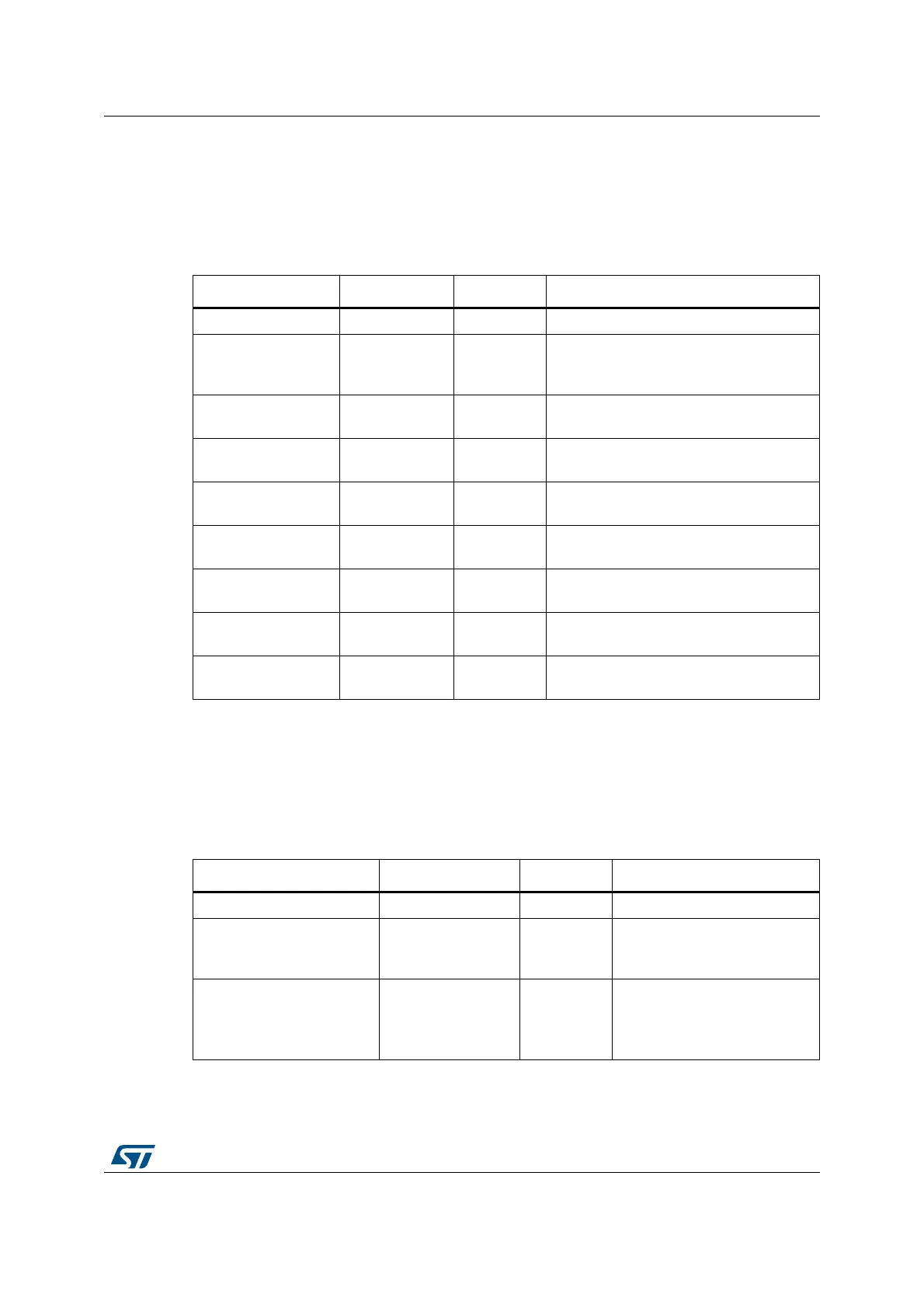

Table 229. Reset events able to generate an update

Source Condition Propagation Comment

Counter roll-over - Yes -

Update event

UPDT in

HRTIM_RSTxR

No

Propagation would result in a lock-up

situation (update causing a reset causing

an update)

External event

EXTEVNTn in

HRTIM_RSTxR

Yes -

TIMy compare

TIMyCMPn in

HRTIM_RSTxR

Yes -

Master compare

MSTCMPn in

HRTIM_RSTxR

Yes -

Master period

MSTPER in

HRTIM_RSTxR

Yes -

Compare 2 and 4

CMPn in

HRTIM_RSTxR

Yes -

Software

TxRST=1 in

HRTIM_CR2

Yes -

HRTIM_SCIN

SYNCRSTx in

HRTIM_TIMxCR

Yes -

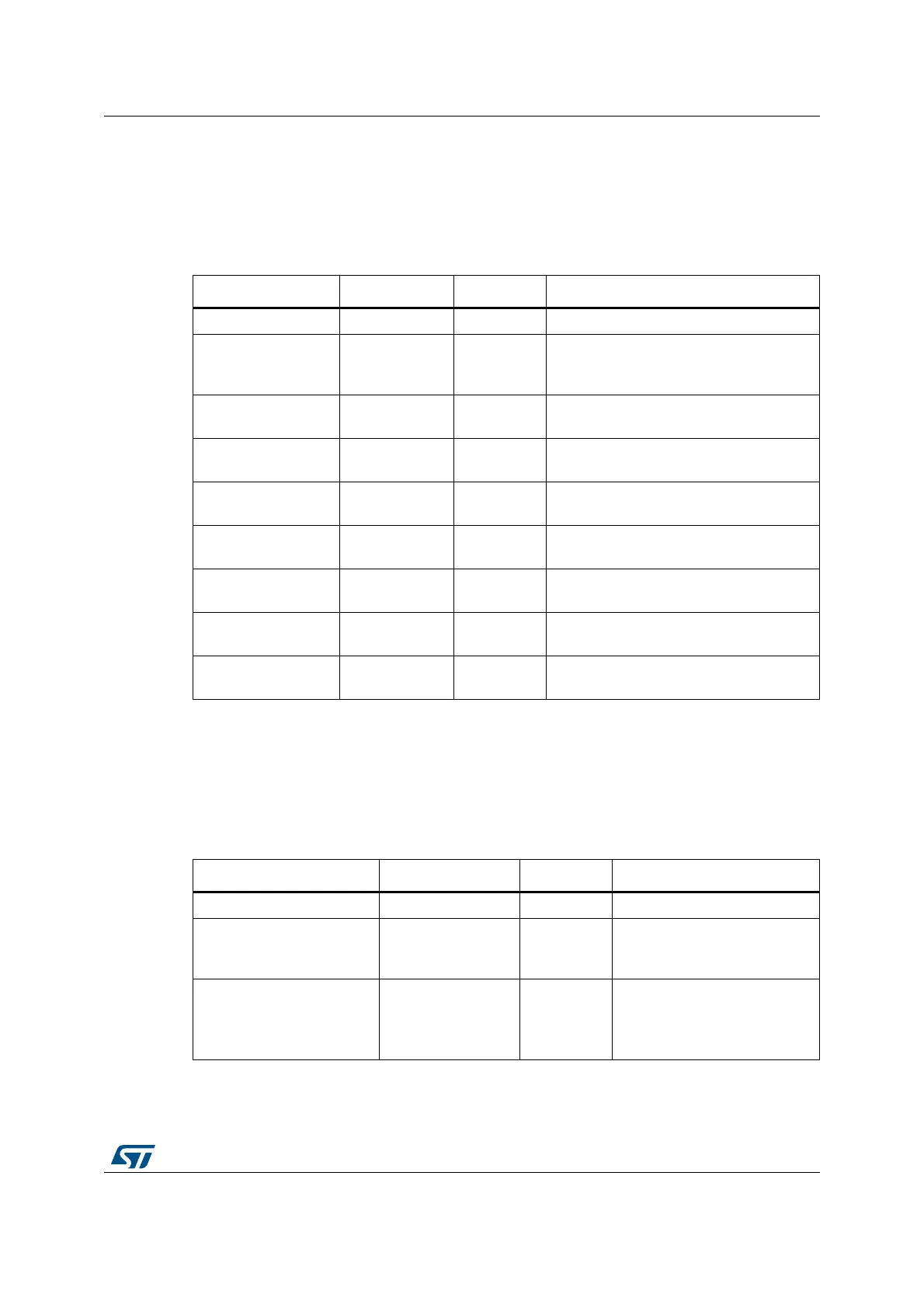

Table 230. Update event propagation for a timer reset

Source Condition Propagation Comment

Burst DMA end UPDGAT[3:0] = 0001 Yes -

Update caused by the

update enable inputs

hrtim_upd_en[3:1]

UPDGAT[3:0] =

0011, 0100, 0101

Yes -

Master update caused by a

roll-over after a burst DMA

MSTU = 1 in

HRTIM_TIMxCR

BRSTDMA[1:0] = 10

in HRTIM_MCR

Yes -

Loading...

Loading...