RM0440 Rev 4 1291/2126

RM0440 General-purpose timers (TIM2/TIM3/TIM4/TIM5)

1343

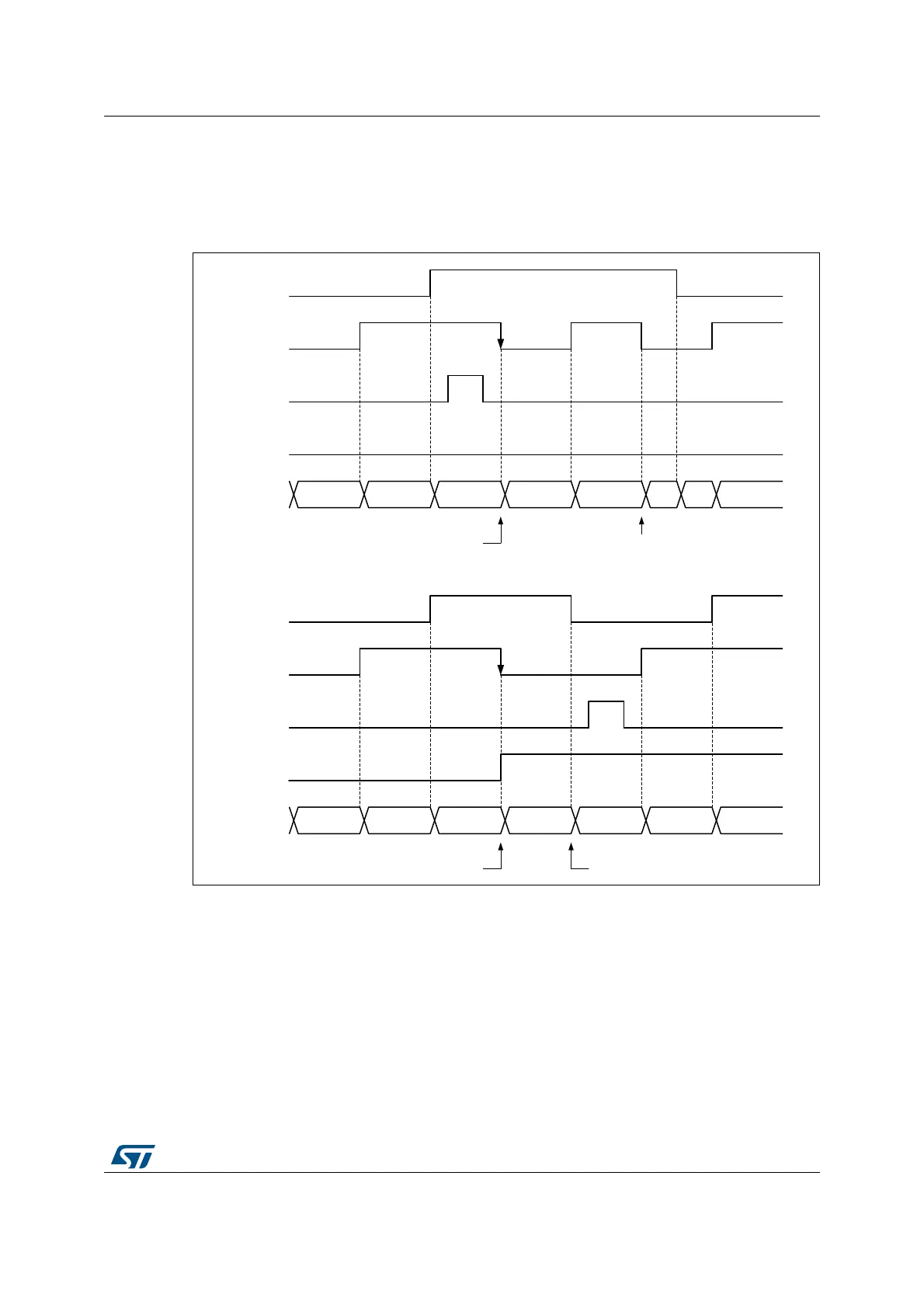

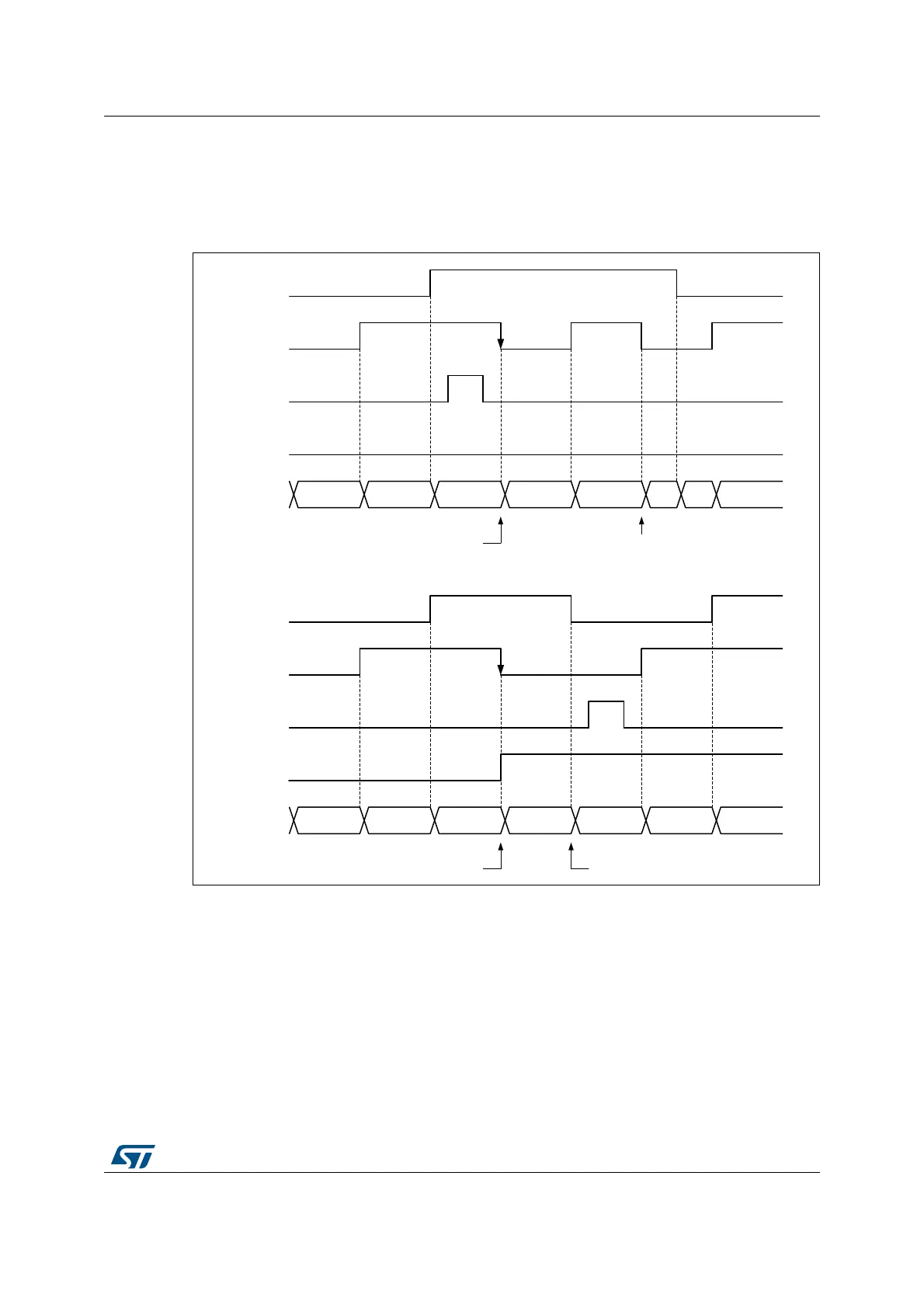

In down-counting mode, the detection is conditioned by a preliminary transition from 1 to 0.

This is to cope with narrow index pulses in gated A and B mode, as shown on Figure 426

below, to avoid any false error detection in case the encoder dithers between TIMx_ARR

and 0 immediately after the index detection.

Figure 426. Down-counting encode error detection

An index error sets the IERRF interrupt flag in the TIMx_SR status register. An index error

interrupt will be generated if the IERRIE bit is set in the TIMx_DIER register.

Functional encoder Interrupts

The following interrupts are also available in encoder mode

• Direction change: any change of the counting direction in encoder mode will cause the

DIR bit in the TIMx_CR1 register to toggle. The direction change sets the DIRF

interrupt flag in the TIMx_SR status register. A direction change interrupt will be

generated if the DIRIE bit is set in the TIMx_DIER register.

• Index event: the Index event sets the IDXF interrupt flag in the TIMx_SR status register.

An Index interrupt will be generated if the IDXIE bit is set in the TIMx_DIER register.

MSv47416V1

Channel A

Channel B

IERRF

Index

Channel A

Channel B

IERRF

Counter

2 1 0 7 0

5

Counter 2 1 0 7 6

4

5

Error detected Error asserted

No error: transition from 0 to

TIMx_ARR following an index

No error: transition from 0 to

TIMx_ARR without index, but not

following a transition from 1 to 0

7 6

Index

Loading...

Loading...