Reset and clock control (RCC) RM0440

278/2126 RM0440 Rev 4

characteristics” section in your device datasheet.

2. The ADC clock can be derived from the AHB clock of the ADC bus interface, divided by a programmable

factor (1, 2 or 4). When the programmable factor is ‘1’, the AHB prescaler must be equal to ‘1’.

7.2.1 HSE clock

The high speed external clock signal (HSE) can be generated from two possible clock

sources:

• HSE external crystal/ceramic resonator

• HSE user external clock

The resonator and the load capacitors have to be placed as close as possible to the

oscillator pins in order to minimize output distortion and startup stabilization time. The

loading capacitance values must be adjusted according to the selected oscillator.

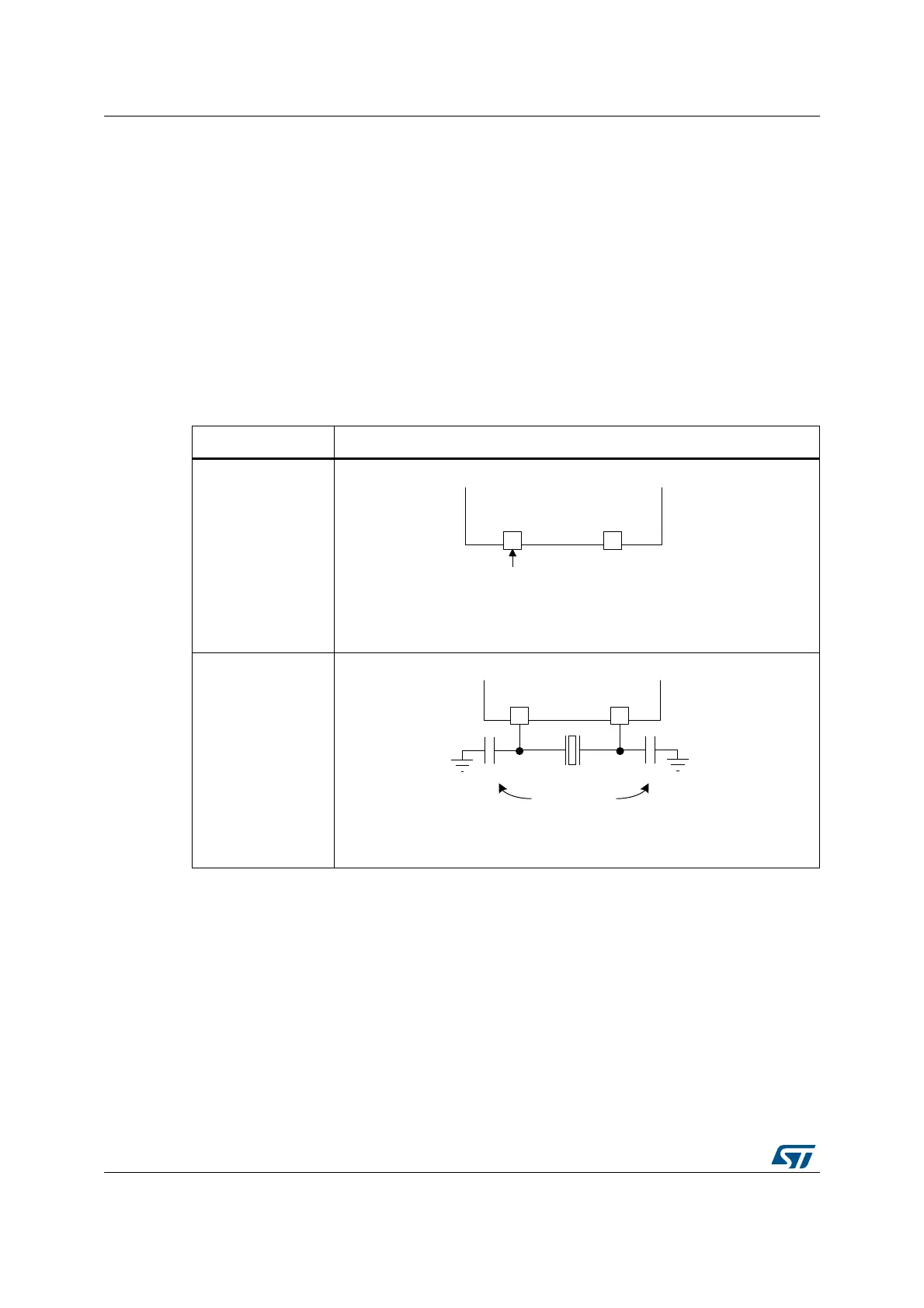

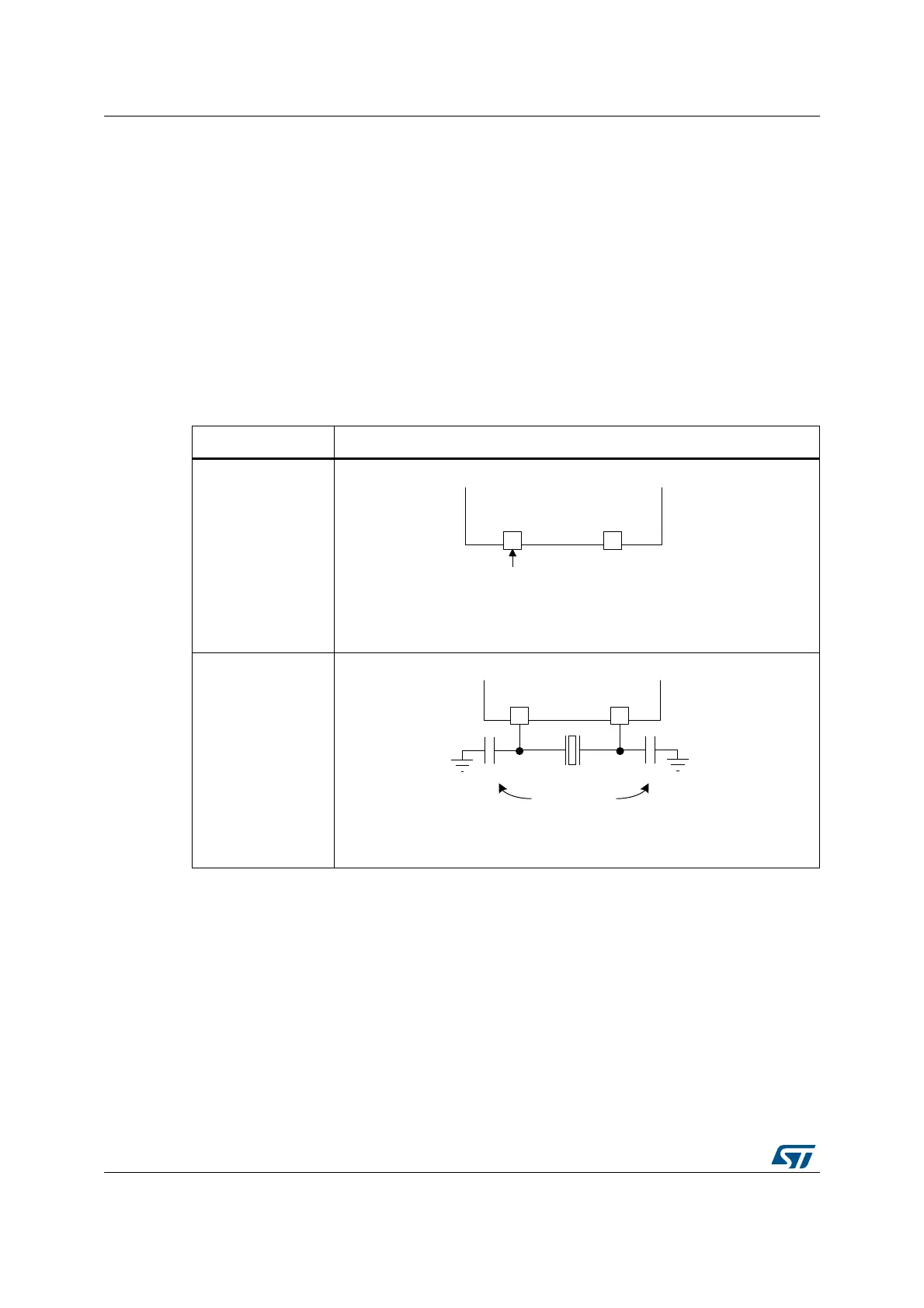

Figure 18. HSE/ LSE clock sources

Clock source Hardware configuration

External clock

Crystal/Ceramic

resonators

MSv31915V1

OSC_IN OSC_OUT

GPIO

External

source

MSv31916V1

OSC_IN OSC_OUT

CL1

CL2

Load

capacitors

Loading...

Loading...