RM0440 Rev 4 1429/2126

RM0440 General-purpose timers (TIM15/TIM16/TIM17)

1445

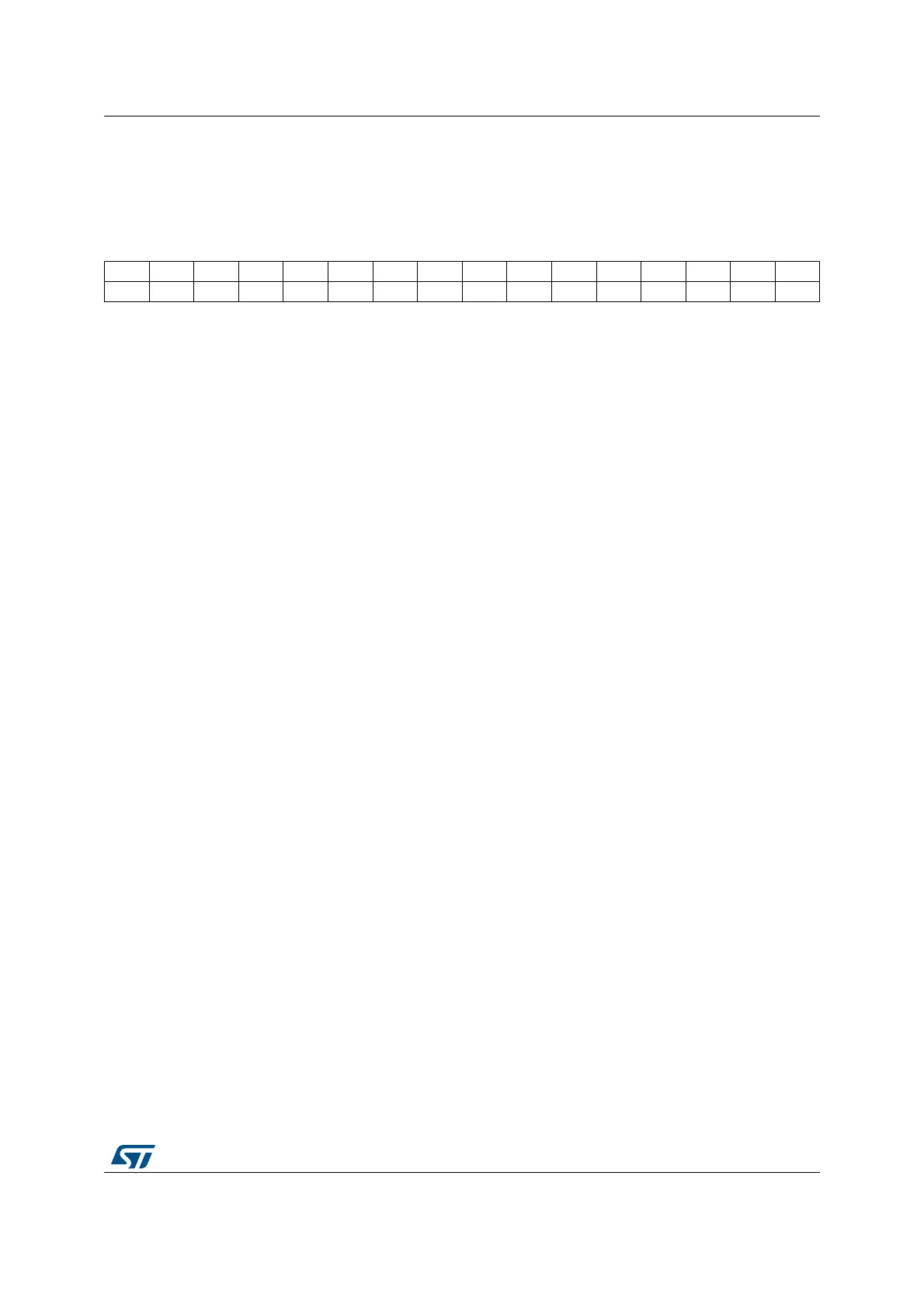

30.8.8 TIMx capture/compare enable register (TIMx_CCER)(x = 16 to 17)

Address offset: 0x20

Reset value: 0x0000

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. CC1NP CC1NE CC1P CC1E

rw rw rw rw

Bits 15:4 Reserved, must be kept at reset value.

Bit 3 CC1NP: Capture/Compare 1 complementary output polarity

CC1 channel configured as output:

0: tim_oc1n active high

1: tim_oc1n active low

CC1 channel configured as input:

This bit is used in conjunction with CC1P to define the polarity of tim_ti1fp1. Refer to the

description of CC1P.

Note: 1. This bit is not writable as soon as LOCK level 2 or 3 has been programmed (LOCK

bits in TIMx_BDTR register) and CC1S=”00” (the channel is configured in output).

2. On channels that have a complementary output, this bit is preloaded. If the CCPC bit

is set in the TIMx_CR2 register then the CC1NP active bit takes the new value from the

preloaded bit only when a commutation event is generated.

Loading...

Loading...