Inter-integrated circuit (I2C) interface RM0440

1926/2126 RM0440 Rev 4

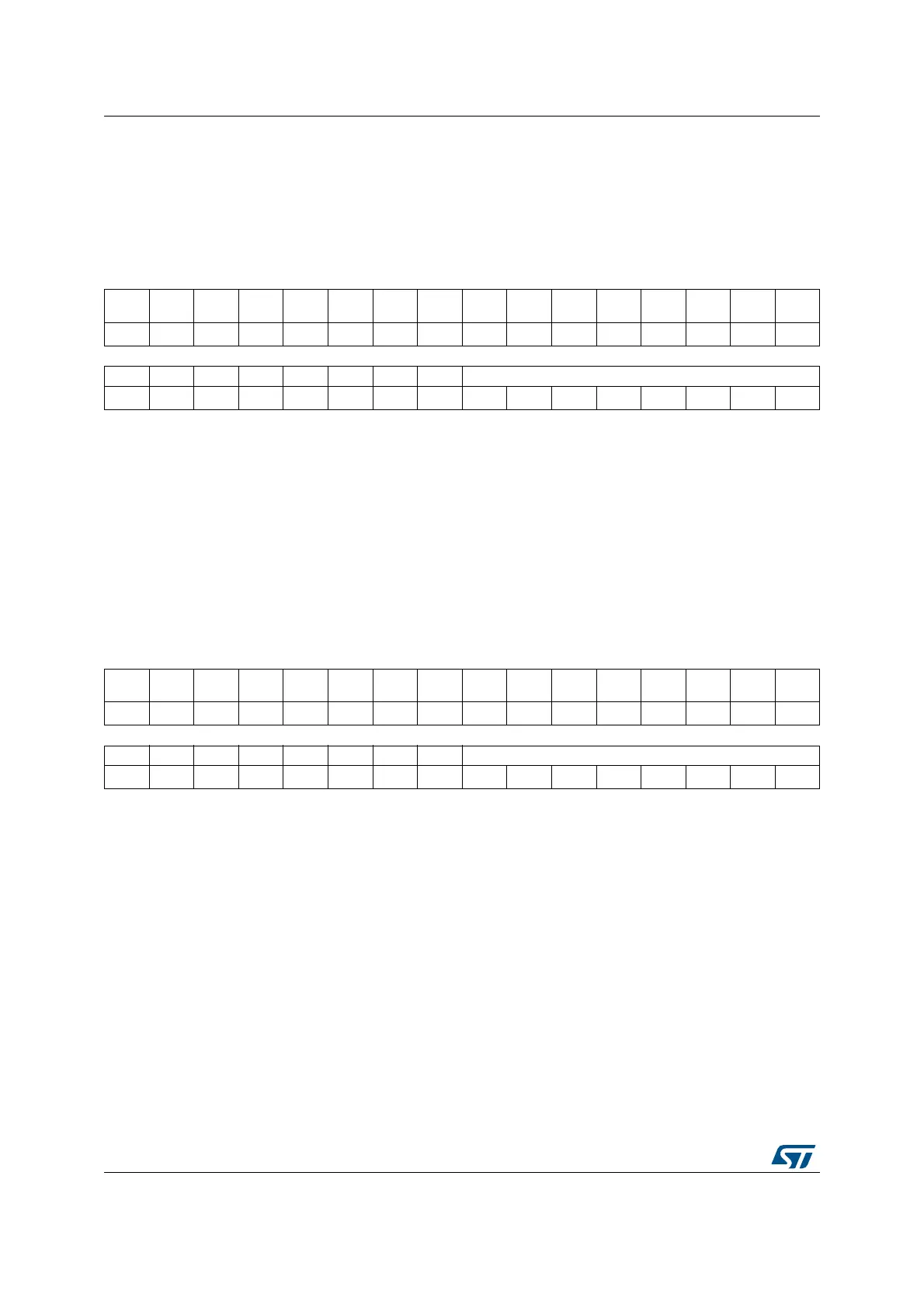

41.7.10 I2C receive data register (I2C_RXDR)

Address offset: 0x24

Reset value: 0x0000 0000

Access: No wait states

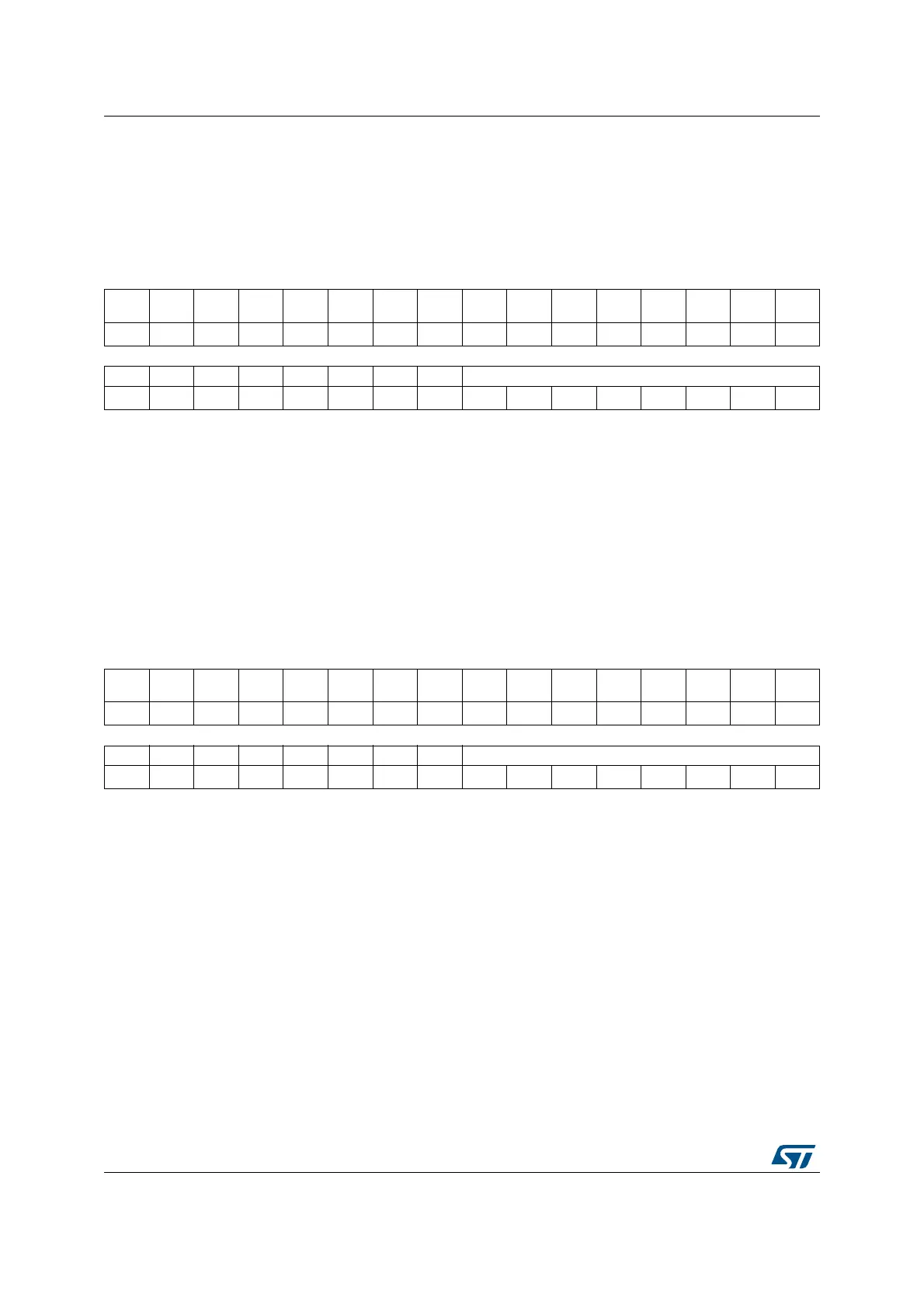

41.7.11 I2C transmit data register (I2C_TXDR)

Address offset: 0x28

Reset value: 0x0000 0000

Access: No wait states

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. RXDATA[7:0]

rrrrrrrr

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 RXDATA[7:0] 8-bit receive data

Data byte received from the I

2

C bus

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. TXDATA[7:0]

rw rw rw rw rw rw rw rw

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 TXDATA[7:0] 8-bit transmit data

Data byte to be transmitted to the I

2

C bus

Note: These bits can be written only when TXE=1.

Loading...

Loading...