Power control (PWR) RM0440

256/2126 RM0440 Rev 4

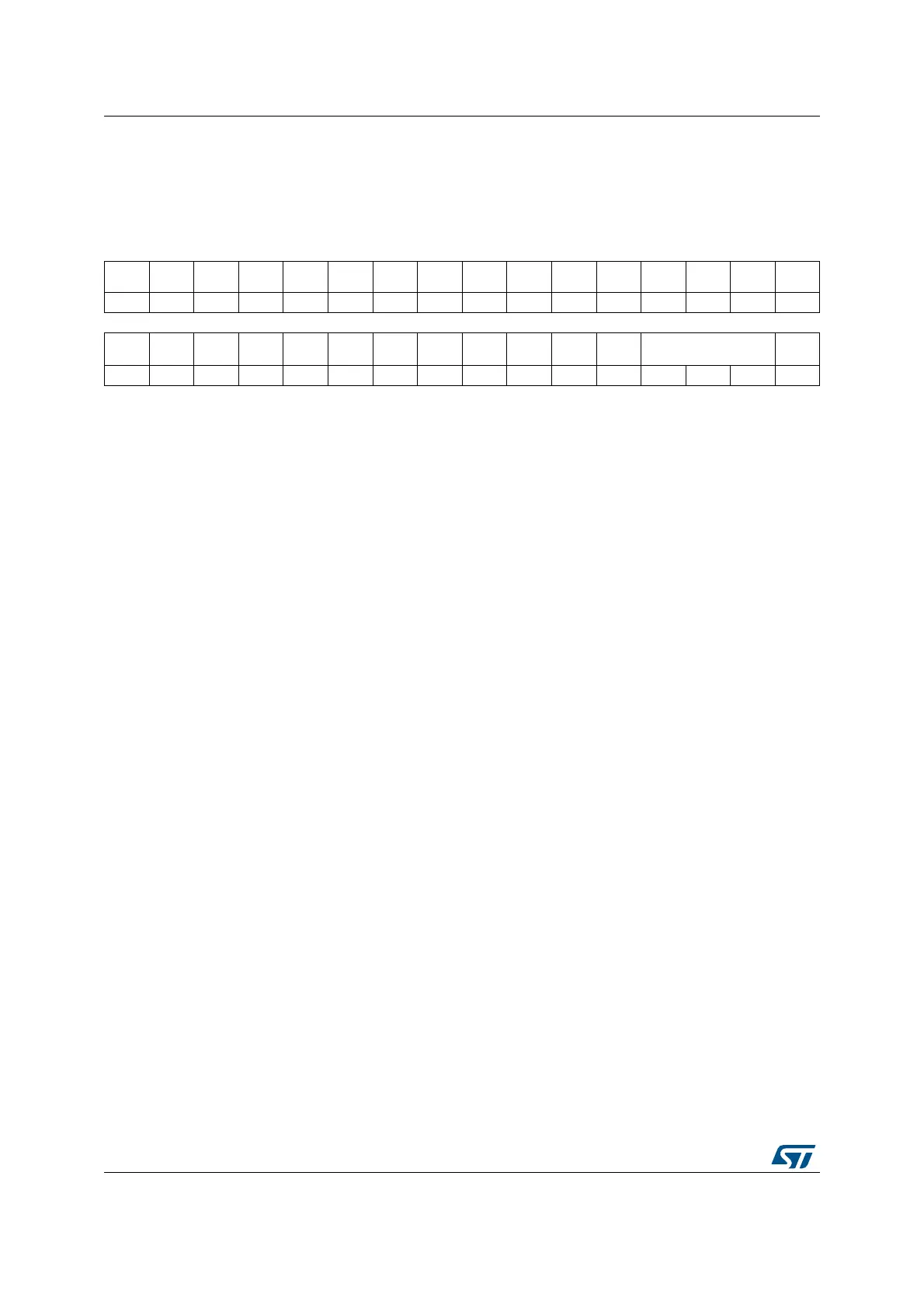

6.4.2 Power control register 2 (PWR_CR2)

Address offset: 0x04

Reset value: 0x0000 0000. This register is reset when exiting Standby mode.

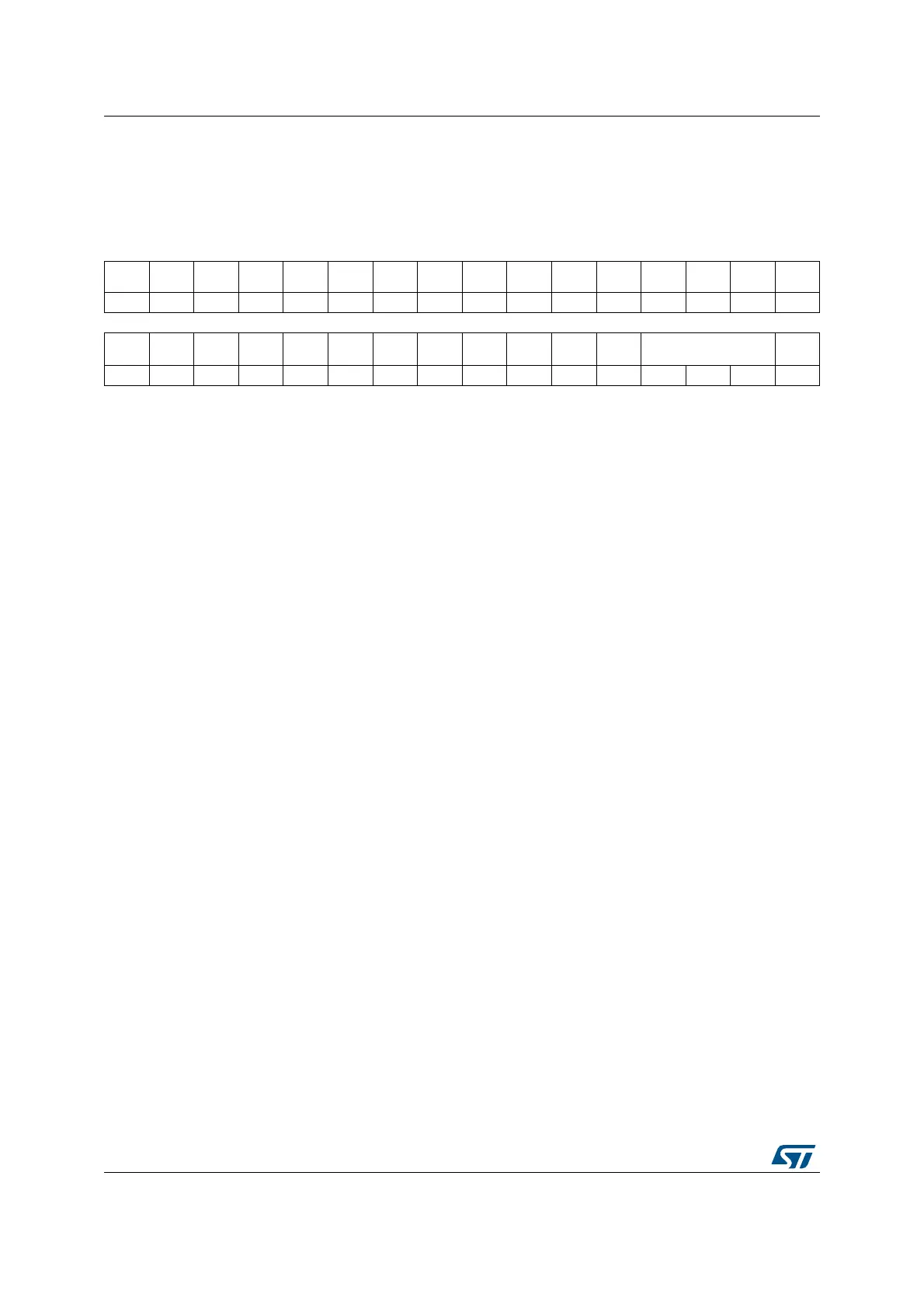

6.4.3 Power control register 3 (PWR_CR3)

Address offset: 0x08

Reset value: 0x0000 8000. This register is not reset when exiting Standby modes and with

the PWRRST bit in the RCC_APB1RSTR1 register.

Access: Additional APB cycles are needed to access this register vs. a standard APB

access (3 for a write and 2 for a read).

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res.

PVME

N2

PVME

N1

Res. Res. PLS[2:0] PVDE

rw rw rw rw rw rw

Bits 31:8 Reserved, must be kept at reset value.

Bit 7 PVMEN2: Peripheral voltage monitoring 4 enable:

V

DDA

vs. DAC 1MSPS /DAC 15MSPS min

voltage.

0: PVM2 (

V

DDA

monitoring vs. 1.8 V threshold) disable.

1: PVM2 (

V

DDA

monitoring vs. 1.8 V threshold) enable.

Bit 6 PVMEN1: Peripheral voltage monitoring 3 enable:

V

DDA

vs. ADC/COMP min voltage 1.62V

0: PVM1 (

V

DDA

monitoring vs. 1.62V threshold) disable.

1: PVM1 (

V

DDA

monitoring vs. 1.62V threshold) enable.

Bits 5:4 Reserved, must be kept at reset value.

Bits 3:1 PLS[2:0]: Programmable voltage detector level selection.

These bits select the PVD falling threshold:

000: V

PVD0

PVD threshold 0

001: V

PVD1

PVD threshold 1

010: V

PVD2

PVD threshold 2

011: V

PVD3

PVD threshold 3

100: V

PVD4

PVD threshold 4

101: V

PVD5

PVD threshold 5

110: V

PVD6

PVD threshold 6

111: External input analog voltage PVD_IN (compared internally to V

REFINT

)

Note: These bits are write-protected when the PVD_LOCK bit is set in the SYSCFG_CFGR2

register. The protection can be reset only by a system reset.

Bit 0 PVDE: Programmable voltage detector enable

0: Programmable voltage detector disable.

1: Programmable voltage detector enable.

Note: This bit is write-protected when the PVD_LOCK bit is set in the SYSCFG_CFGR2

register. The protection can be reset only by a system reset.

Loading...

Loading...