Reset and clock control (RCC) RM0440

296/2126 RM0440 Rev 4

7.4.5 Clock interrupt enable register (RCC_CIER)

Address offset: 0x18

Reset value: 0x0000 0000

Access: no wait state, word, half-word and byte access

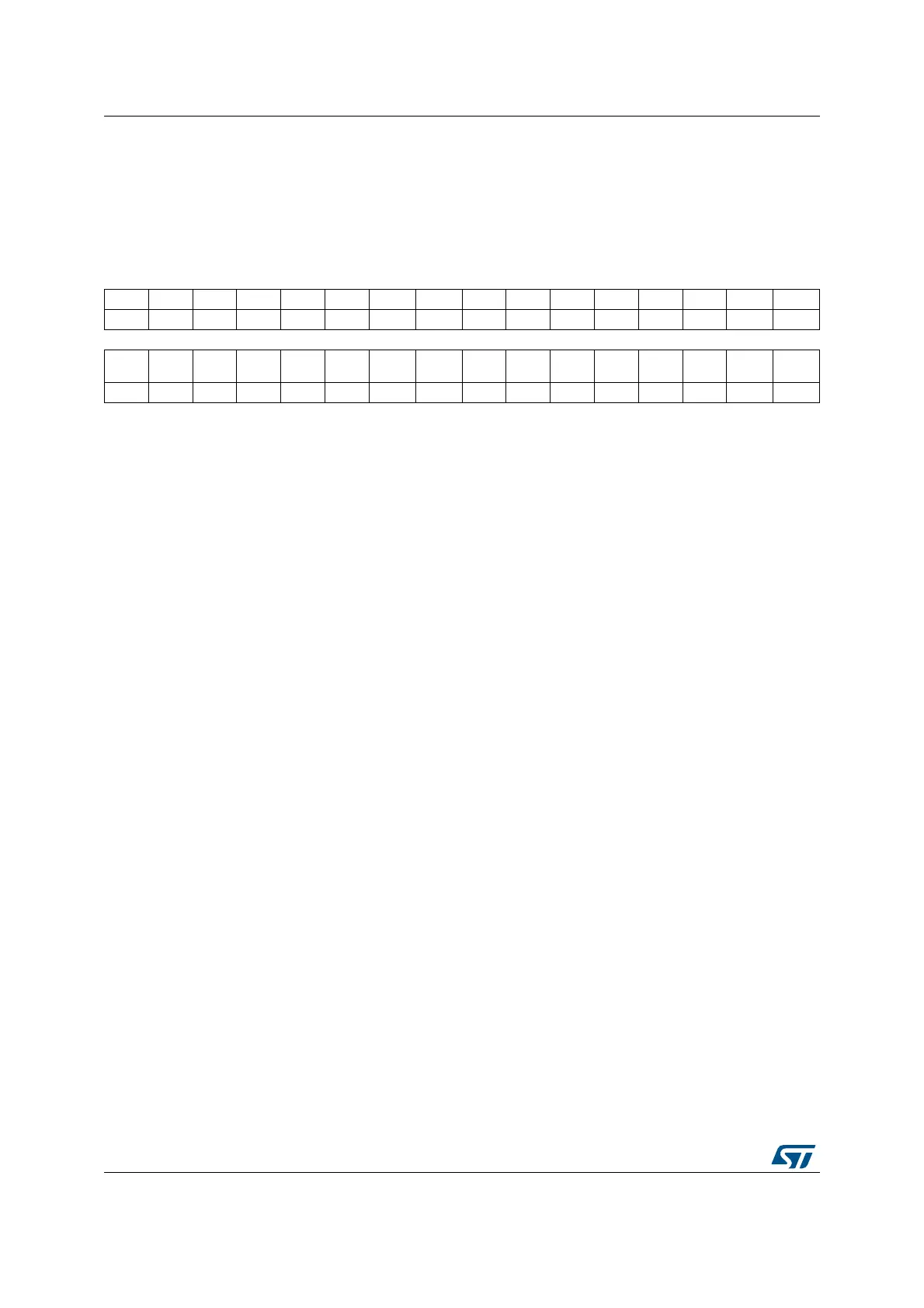

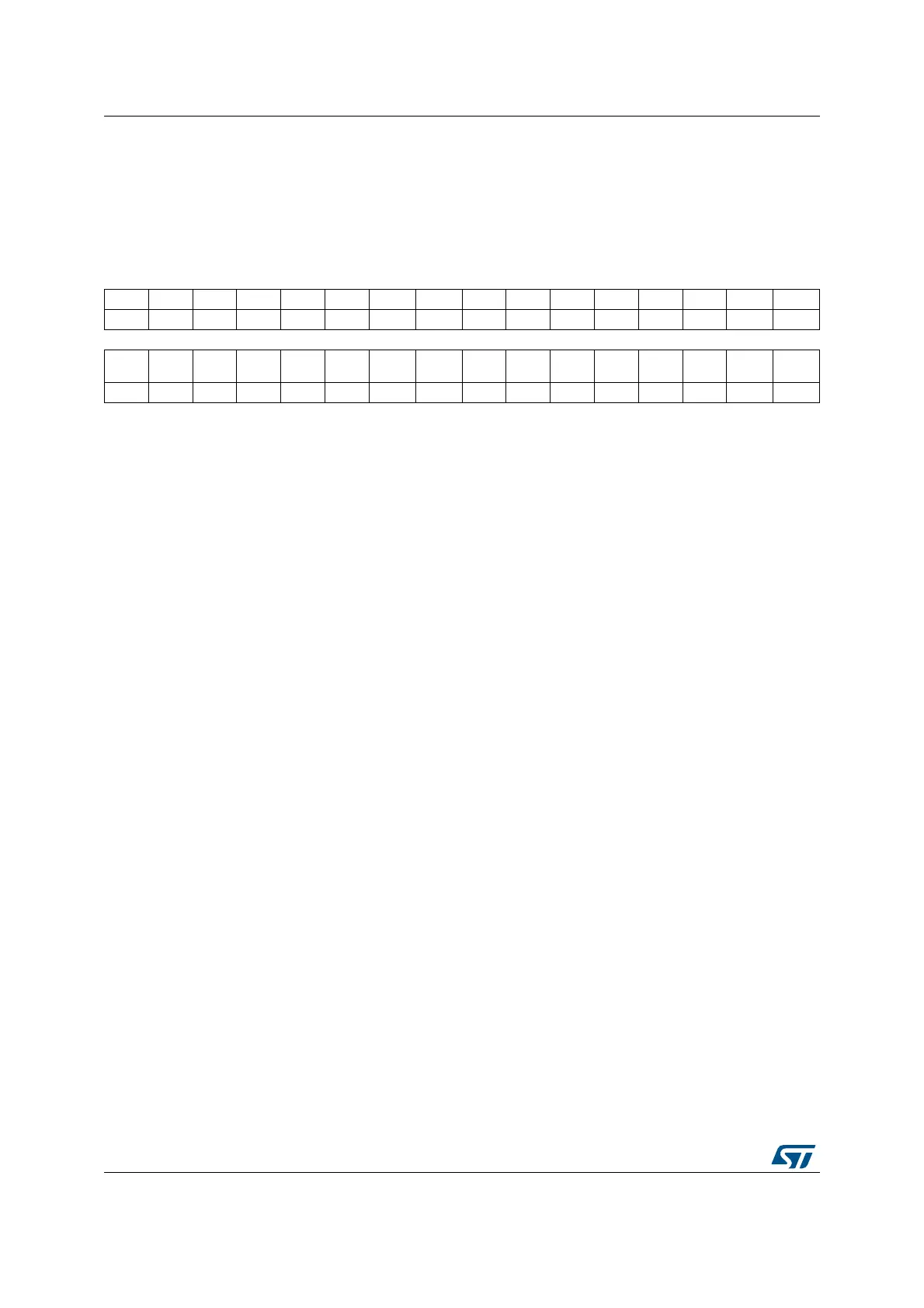

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109 8 765432 1 0

Res. Res. Res. Res. Res.

HSI48

RDYIE

LSE

CSSIE

Res. Res. Res.

PLL

RDYIE

HSE

RDYIE

HSI

RDYIE

Res.

LSE

RDYIE

LSI

RDYIE

rw rw rw rw rw rw rw

Bits 31:11 Reserved, must be kept at reset value.

Bit 10 HSI48RDYIE: HSI48 ready interrupt enable

Set and cleared by software to enable/disable interrupt caused by the internal HSI48

oscillator.

0: HSI48 ready interrupt disabled

1: HSI48 ready interrupt enabled

Bit 9 LSECSSIE: LSE clock security system interrupt enable

Set and cleared by software to enable/disable interrupt caused by the clock security system

on LSE.

0: Clock security interrupt caused by LSE clock failure disabled

1: Clock security interrupt caused by LSE clock failure enabled

Bits 8:6 Reserved, must be kept at reset value.

Bit 5 PLLRDYIE: PLL ready interrupt enable

Set and cleared by software to enable/disable interrupt caused by PLL lock.

0: PLL lock interrupt disabled

1: PLL lock interrupt enabled

Bit 4 HSERDYIE: HSE ready interrupt enable

Set and cleared by software to enable/disable interrupt caused by the HSE oscillator

stabilization.

0: HSE ready interrupt disabled

1: HSE ready interrupt enabled

Bit 3 HSIRDYIE: HSI16 ready interrupt enable

Set and cleared by software to enable/disable interrupt caused by the HSI16 oscillator

stabilization.

0: HSI16 ready interrupt disabled

1: HSI16 ready interrupt enabled

Loading...

Loading...