General-purpose timers (TIM15/TIM16/TIM17) RM0440

1438/2126 RM0440 Rev 4

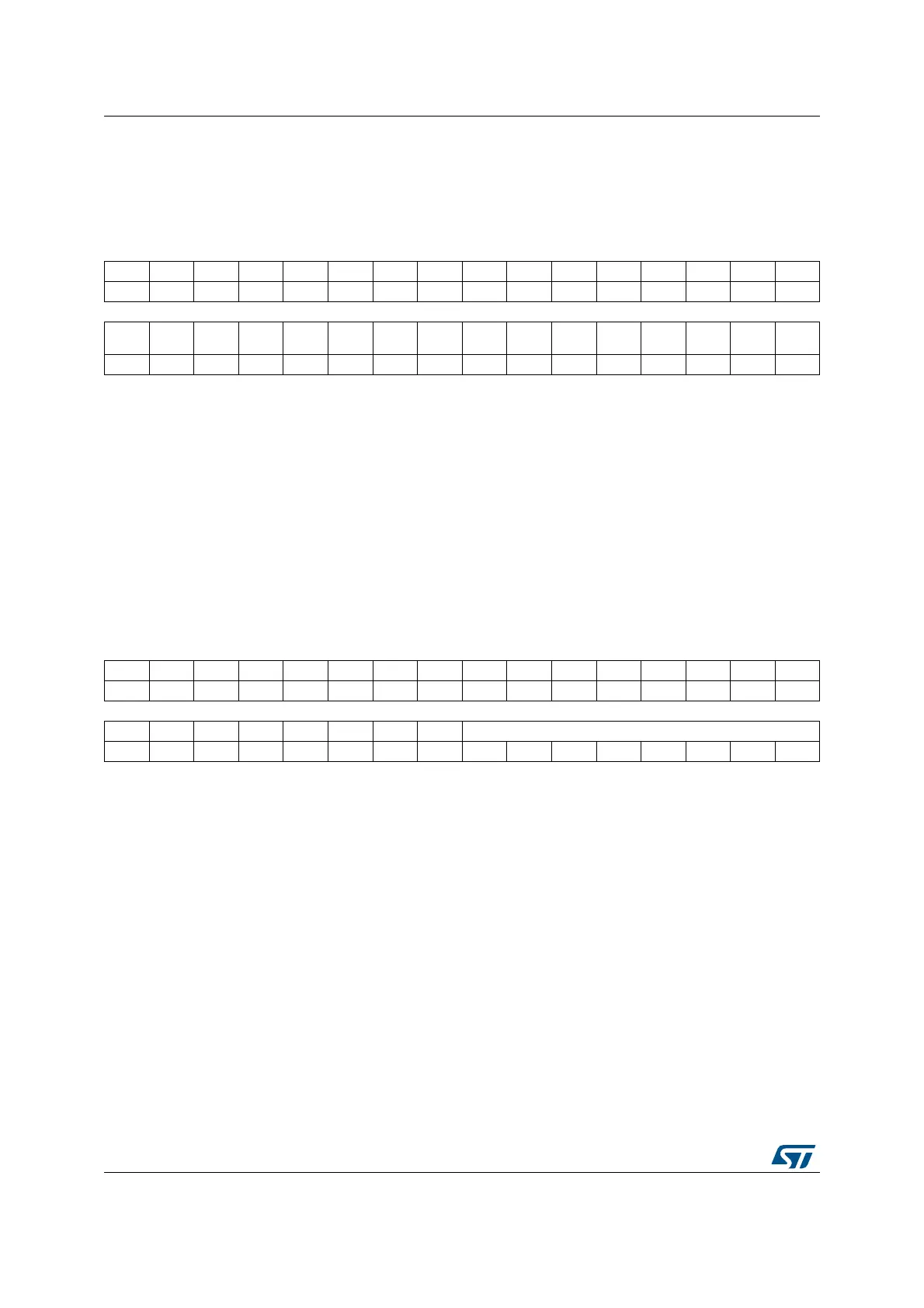

30.8.15 TIMx option register 1 (TIMx_OR1)(x = 16 to 17)

Address offset: 0x50

Reset value: 0x0000 0000

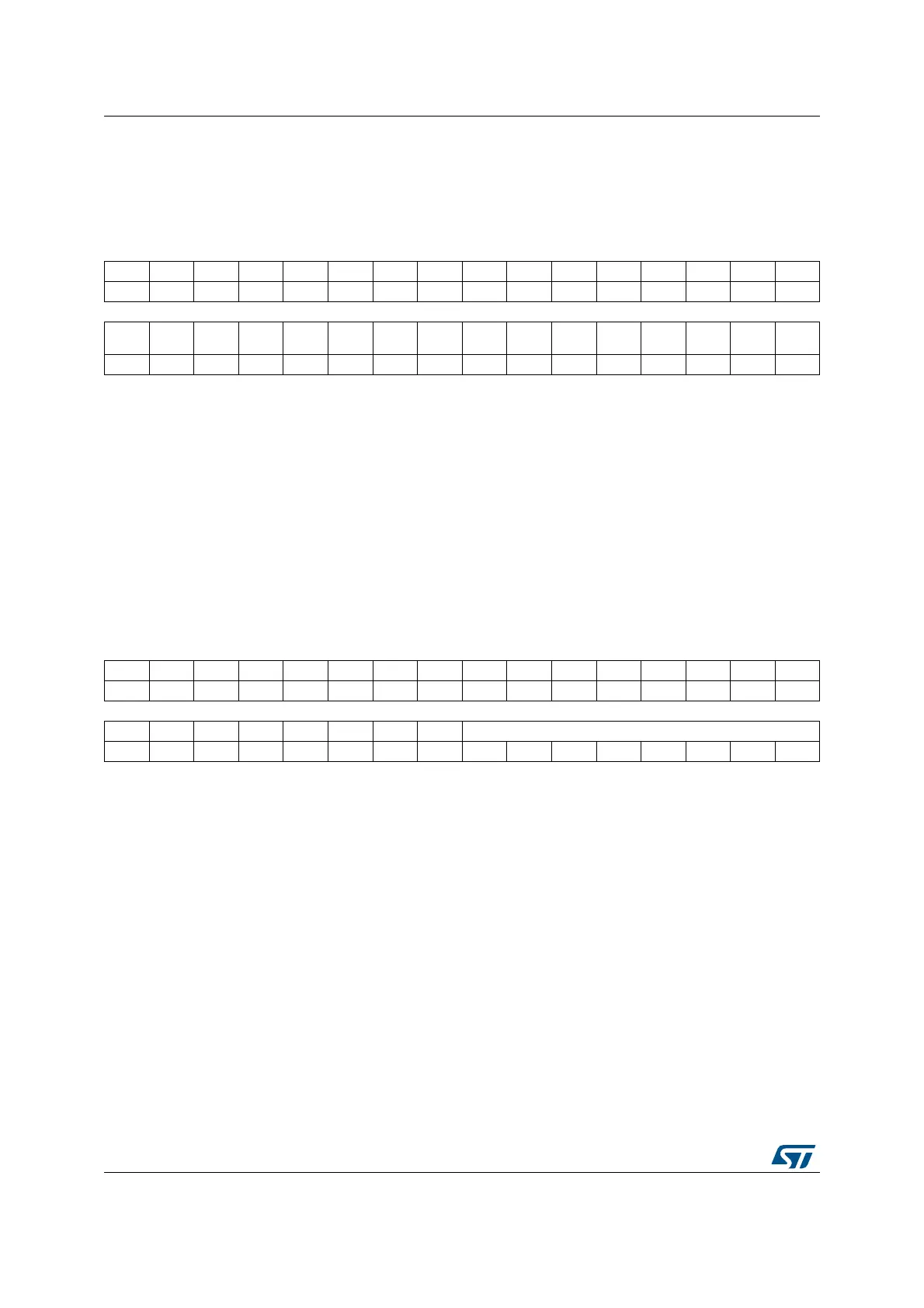

30.8.16 TIMx timer deadtime register 2 (TIMx_DTR2)(x = 16 to 17)

Address offset: 0x054

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

HSE32

EN

rw

Bits 31:1 Reserved, must be kept at reset value.

Bit 0 HSE32EN: HSE Divided by 32 enable

This bit enables the HSE divider by 32 for the tim_ti1_in3. See Table 288: Interconnect to the

tim_ti1 input multiplexer for details.

0: HSE divided by 32 disabled

1: HSE divided by 32 enabled

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. DTPE DTAE

rw rw

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. DTGF[7:0]

rw rw rw rw rw rw rw rw

Bits 31:18 Reserved, must be kept at reset value.

Bit 17 DTPE: Deadtime preload enable

0: Deadtime value is not preloaded

1: Deadtime value preload is enabled

Note: This bit can not be modified as long as LOCK level 1, 2 or 3 has been programmed

(LOCK bits in TIMx_BDTR register).

Bit 16 DTAE: Deadtime asymmetric enable

0:Deadtime on rising and falling edges are identical, and defined with DTG[7:0] register

1:Deadtime on rising edge is defined with DTG[7:0] register and deadtime on falling edge is

defined with DTGF[7:0] bits.

Note: This bit can not be modified as long as LOCK level 1, 2 or 3 has been programmed

(LOCK bits in TIMx_BDTR register).

Bits 15:8 Reserved, must be kept at reset value.

Loading...

Loading...