General-purpose timers (TIM15/TIM16/TIM17) RM0440

1442/2126 RM0440 Rev 4

30.8.19 TIMx alternate function register 2 (TIMx_AF2)(x = 16 to 17)

Address offset: 0x064

Reset value: 0x0000 0000

30.8.20 TIMx DMA control register (TIMx_DCR)(x = 16 to 17)

Address offset: 0x3DC

Reset value: 0x0000 0000

Bit 0 BKINE: TIMx_BKIN input enable

This bit enables the TIMx_BKIN alternate function input for the timer’s tim_brk input.

TIMx_BKIN input is ‘ORed’ with the other tim_brk sources.

0: TIMx_BKIN input disabled

1: TIMx_BKIN input enabled

Note: This bit can not be modified as long as LOCK level 1 has been programmed (LOCK bits

in TIMx_BDTR register).

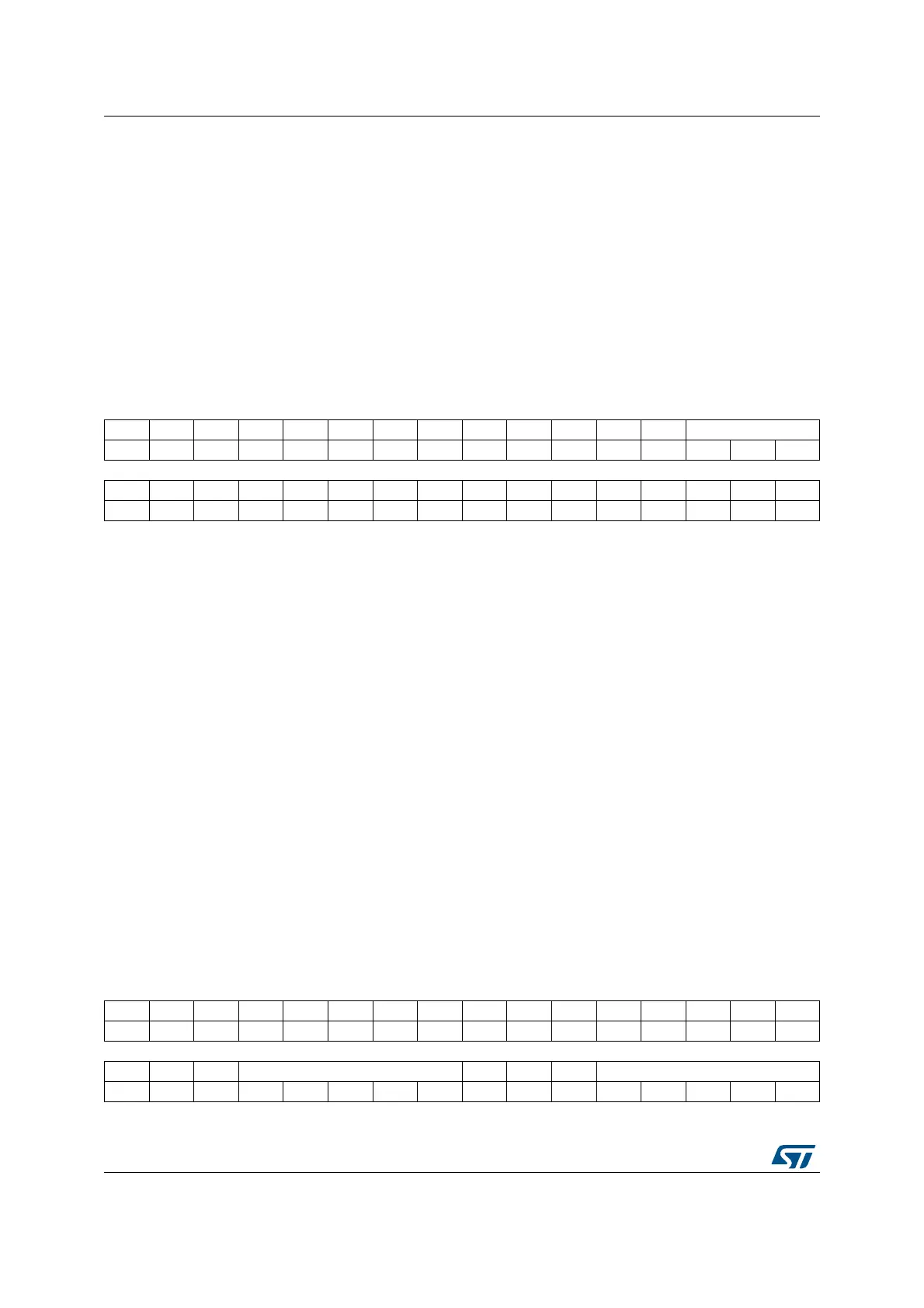

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. OCRSEL[2:0]

rw rw rw

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

Bits 31:19 Reserved, must be kept at reset value.

Bits 18:16 OCRSEL[2:0]: tim_ocref_clr source selection

These bits select the tim_ocref_clr input source.

000: tim_ocref_clr0

001: tim_ocref_clr1

010: tim_ocref_clr2

011: tim_ocref_clr3

100: tim_ocref_clr4

101: tim_ocref_clr5

110: tim_ocref_clr6

111: tim_ocref_clr7

Refer to Section 30.4.2: TIM15/TIM16/TIM17 pins and internal signals for product specific

implementation.

Note: These bits can not be modified as long as LOCK level 1 has been programmed (LOCK

bits in TIMx_BDTR register).

Bits 15:0 Reserved, must be kept at reset value.

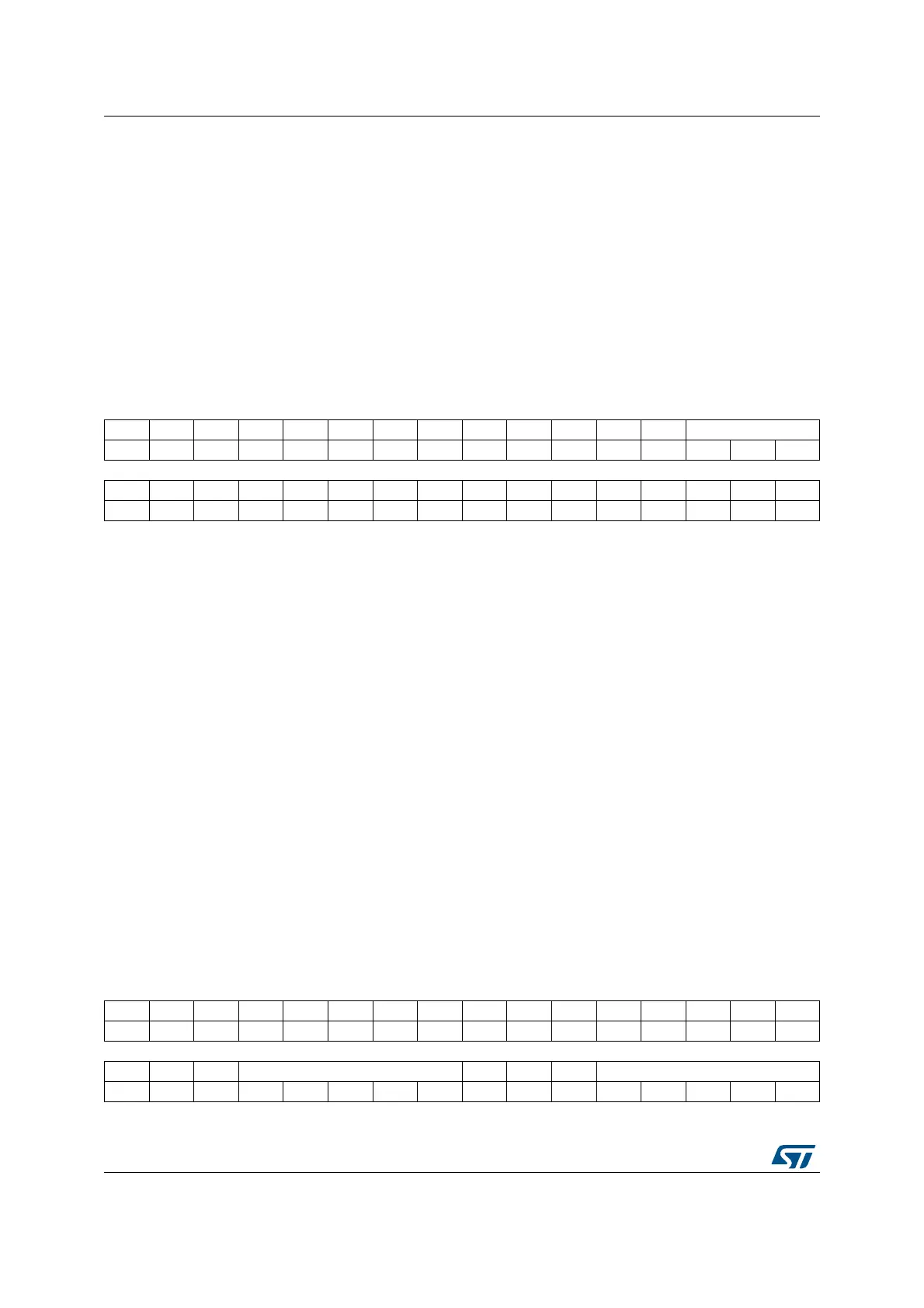

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. DBL[4:0] Res. Res. Res. DBA[4:0]

rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...