STC8A8K64D4 Series Manual

-

0: disable comparator falling-edge interrupt.

1: enable comparator falling-edge interrupt.

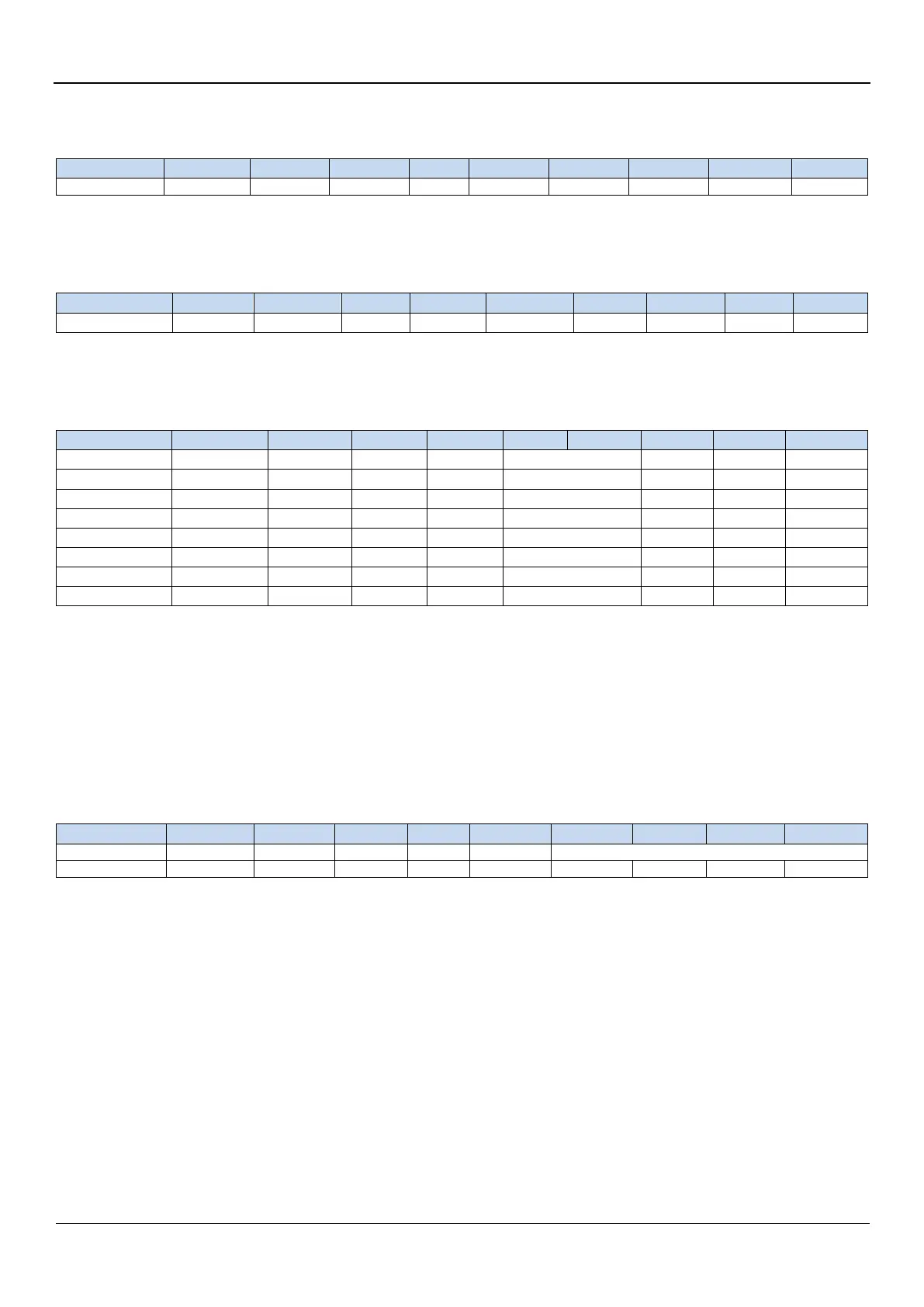

Enhanced PWM Configuration Register

EPWMCBI: Enhanced PWM0 counter interrupt enable bit.

0: disable PWM0 counter interrupt

1: enable PWM0 counter interrupt

Enhanced PWM Abnormal Detection Control Register

EFDI: PWM external abnormal event interrupt enable bit.

0: disable PWM external abnormal event interrupt

1: enable PWM external abnormal event interrupt

Enhanced PWM Control Register

ENI: PWM channel interrupt enable bit.

0: disable PWM interrupt

1: enable PWM interrupt

ENT2SI: PWM channel 2nd trigger point interrupt enable bit.

0: disable the 2nd trigger point interrupt of PWM

1: enable the 2nd trigger point interrupt of PWM

ENT1SI: PWM channel 1st trigger point interrupt enable bit.

0: disable the 1st trigger point interrupt of PWM

1: enable the 1st trigger point interrupt of PWM

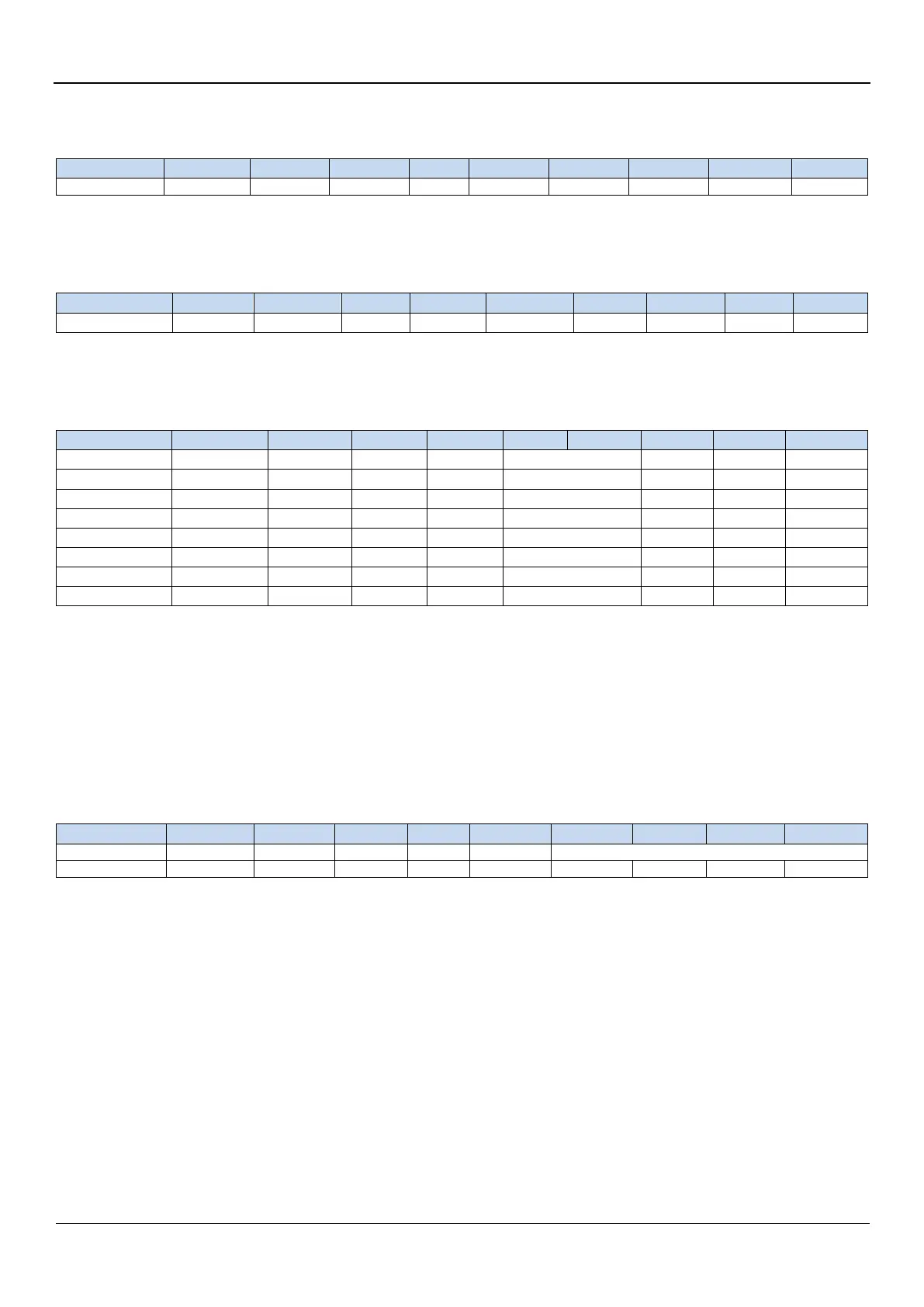

I2C Control Registers

EMSI: I

2

C master mode interrupt enable bit.

0: disable I

2

C master mode interrupt.

1: enable I

2

C master mode interrupt.

ESTAI: I

2

C slave receives the START event interrupt enable bit.

0: disable I

2

C slave receives the START event interrupt.

1: enable I

2

C slave receives the START event interrupt.

ERXI: I

2

C slave completes receiving data event interrupt enable bit.

0: disable I

2

C slave completes receiving data event interrupt.

1: enable I

2

C slave completes receiving data event interrupt.

ETXI: I

2

C slave completes transmitting data event interrupt enable bit.

0: disable I

2

C slave completes transmitting data event interrupt.

1: enable I

2

C slave completes transmitting data event interrupt.

ESTOI: I

2

C slave receives STOP event interrupt enable bit.

0: disable I

2

C slave receives STOP event interrupt.

1: enable I

2

C slave receives STOP event interrupt.

Port interrupt enable registers

Loading...

Loading...