Arbitration

is

very simple. Fat Agnus tells the bus control prior to taking the

display RAM buses by asserting an input to the control chip (GARY) called /

DBR. Whenever Fat Agnus has the display buses and the 68000 wants them, the

68000

is

held

off

by not giving

it

/DTACK.

In

this state the 68000 has no effect

on the display buses until the bus controller enables the bus drivers.

Fat Agnus generates the DRAM timings and does all address mUltiplexing.

If

the

68000

is

running a video memory cycle, its addresses are routed through Fat

Agnus onto the multiplexed address lines.

If

the custom chips are running a

memory cycle the addresses are routed to the multiplexed address lines from

internal address register.

Display

RAM

The display RAM

is

a

5I2K

read/write memory that resides on the RAM address

and RAM data buses. It

is

expandable to

1M

bytes by the addition

of

the RAM

expansion module. It

is

implemented using standard 256K x 1 dynamic RAMs,

refreshed by Fat Agnus.

The display RAM

is

really used for much more than just holding graphics data.

It

also stores code and data for the 68000.

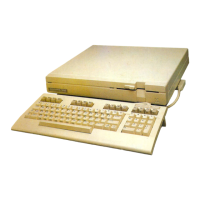

Custom Control Chips

The Amiga's animation, graphics and sound are produced by three custom chips.

Fat Agnus (8370), Denise (8362) and Paula (8364). A fourth custom chip, Gary

serves as the control chip. The following pages include pin diagrams, feature

lists, and block diagrams for these chips.

Technical Reference

A-I5