Keysight E4980A/AL Precision LCR Meter 267

Overview of Remote Control

Status Byte

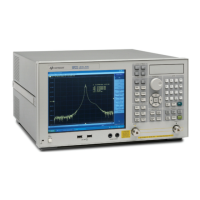

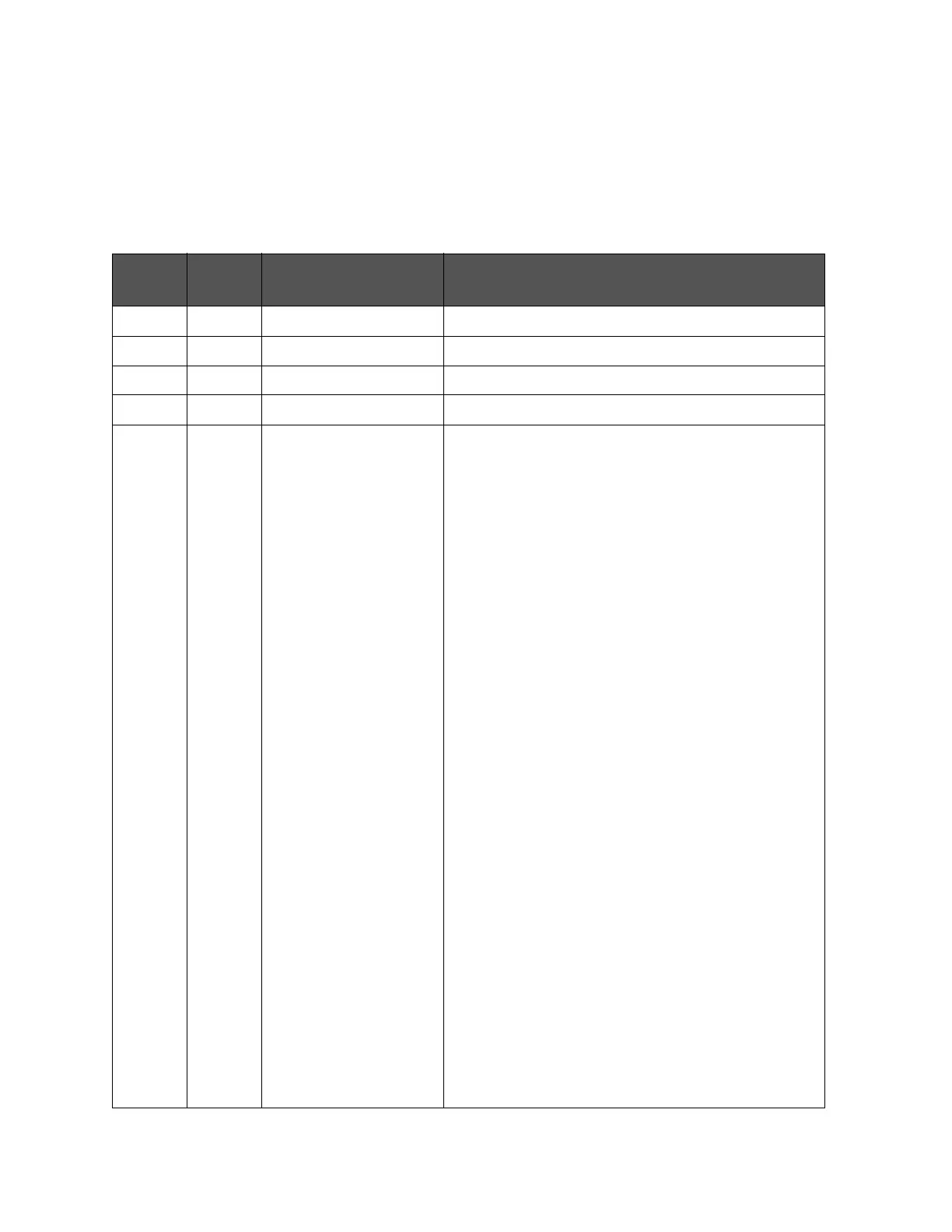

Table 8-1 gives the individual bit assignments of the status byte and its bit

weights. When you read the status byte using GPIB serial polling, the value is

the sum of the total bit weights of all the high bits existing at the time you read

the byte. After serial polling of the status byte, only bit 6 (RQS) is cleared.

Table 8-1 Status Bit definition of the Status Byte Register

Bit No. Bit

Weight

Name Description

0 1 unused always 0 (zero)

1 2 unused always 0 (zero)

2 4 unused always 0 (zero)

3 8 unused always 0 (zero)

4 16 MAV (message available) This bit is set to “1” when the E4980A/AL has available data to output

that have not been read yet. This bit is reset to “0” when all the data

have been retrieved. (This bit is not cleared by serial polling.)

5 32 Standard Event Status Register

Summary

This bit is set to “1” when any enabled bits of the standard event status

register have been set to “1.” This bit is cleared when all bits of the

standard event status register are set to “0.” (This bit is not cleared by

serial polling).

6 64 RQS Bit 6 serves two functions (RQS/MSS), depending on how it is read.

RQS (Request Service) Bit

If bit 6 is read in the serial polling process, it is treated as an RQS bit

and is reset during the serial polling process.

MSS (Master Summary) Bit

If bit 6 is read using the *STB? (status byte) query, it is treated as an

MSS bit, and its value is not changed by executing the *STB? query.

To understand this operation, think of the RQS and MSS bits as two

inputs to a multiplexer (MUX) and the output of the MUX being bit 6 of

the status byte register.

During the serial polling operation the MUX path selected is from the

service request generation circuit to bit 6, so bit 6 represents the RQS

bit.

During execution of the *STB? query the MUX path selected is from

the master summary bit generation circuit to bit 6, so bit 6 represents

the MSS bit.

To clear the MSS bit, all bits of the original registers corresponding to

the enabled summary bit in the status byte and the output buffer of the

E4980A/AL must be cleared. When you read the status byte including

the MSS bit instead of the RQS bit, the *STB? query must be used. The

*STB? query clears neither the MSS bit nor the RQS bit.

7 128 Operation Status Register

Summary

This bit is set to “1” when one or more enabled bits of the operation

status register is set to “1.” This bit is cleared when all bits of the

operation status register are set to 0. (This bit is not cleared by serial

polling.)

Loading...

Loading...