Low-power timer (LPTIM) RM0440

1478/2126 RM0440 Rev 4

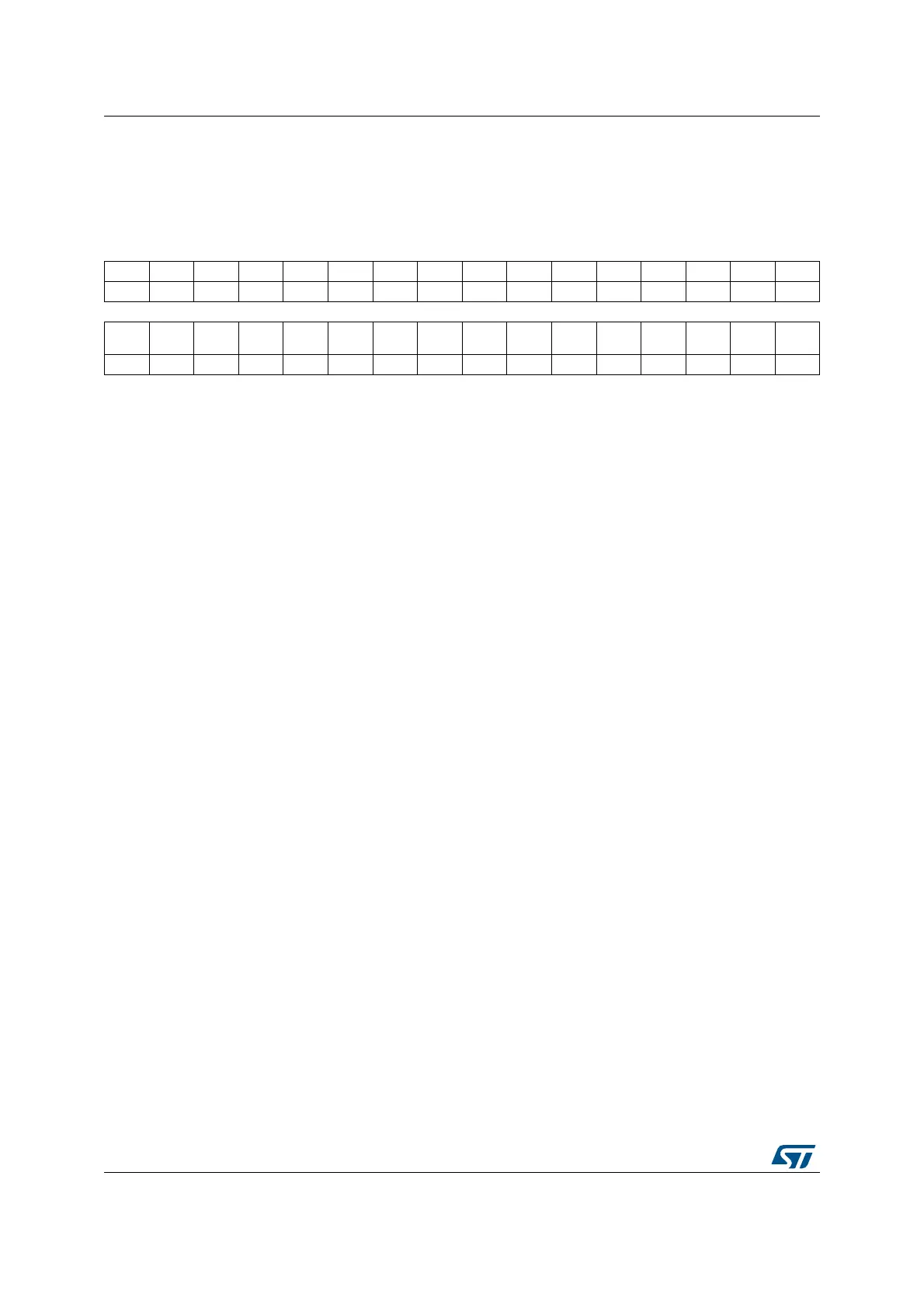

32.7.1 LPTIM interrupt and status register (LPTIM_ISR)

Address offset: 0x000

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. DOWN UP

ARR

OK

CMP

OK

EXT

TRIG

ARRM CMPM

rrrrrrr

Bits 31:7 Reserved, must be kept at reset value.

Bit 6 DOWN: Counter direction change up to down

In Encoder mode, DOWN bit is set by hardware to inform application that the counter direction has

changed from up to down. DOWN flag can be cleared by writing 1 to the DOWNCF bit in the

LPTIM_ICR register.

Note: If the LPTIM does not support encoder mode feature, this bit is reserved. Please refer to

Section 32.3: LPTIM implementation.

Bit 5 UP: Counter direction change down to up

In Encoder mode, UP bit is set by hardware to inform application that the counter direction has

changed from down to up. UP flag can be cleared by writing 1 to the UPCF bit in the LPTIM_ICR

register.

Note: If the LPTIM does not support encoder mode feature, this bit is reserved. Please refer to

Section 32.3: LPTIM implementation.

Bit 4 ARROK: Autoreload register update OK

ARROK is set by hardware to inform application that the APB bus write operation to the LPTIM_ARR

register has been successfully completed. ARROK flag can be cleared by writing 1 to the ARROKCF

bit in the LPTIM_ICR register.

Bit 3 CMPOK: Compare register update OK

CMPOK is set by hardware to inform application that the APB bus write operation to the

LPTIM_CMP register has been successfully completed.

Bit 2 EXTTRIG: External trigger edge event

EXTTRIG is set by hardware to inform application that a valid edge on the selected external trigger

input has occurred. If the trigger is ignored because the timer has already started, then this flag is

not set. EXTTRIG flag can be cleared by writing 1 to the EXTTRIGCF bit in the LPTIM_ICR register.

Bit 1 ARRM: Autoreload match

ARRM is set by hardware to inform application that LPTIM_CNT register’s value reached the

LPTIM_ARR register’s value. ARRM flag can be cleared by writing 1 to the ARRMCF bit in the

LPTIM_ICR register.

Bit 0 CMPM: Compare match

The CMPM bit is set by hardware to inform application that LPTIM_CNT register value reached the

LPTIM_CMP register’s value.

Loading...

Loading...