RM0440 Rev 4 1485/2126

RM0440 Low-power timer (LPTIM)

1487

Caution: The LPTIM_CMP register must only be modified when the LPTIM is enabled (ENABLE bit

set to ‘1’).

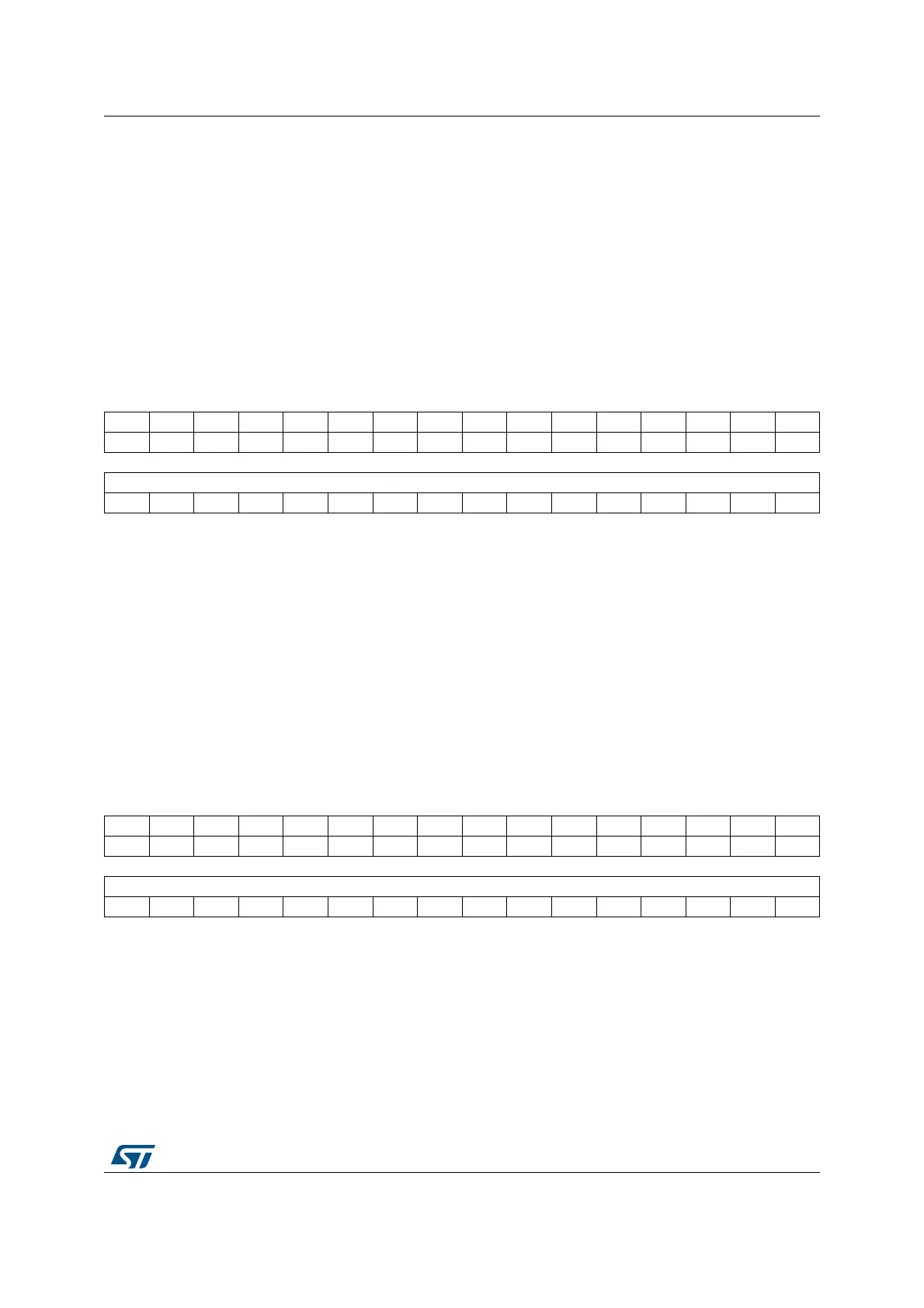

32.7.7 LPTIM autoreload register (LPTIM_ARR)

Address offset: 0x018

Reset value: 0x0000 0001

Caution: The LPTIM_ARR register must only be modified when the LPTIM is enabled (ENABLE bit

set to ‘1’).

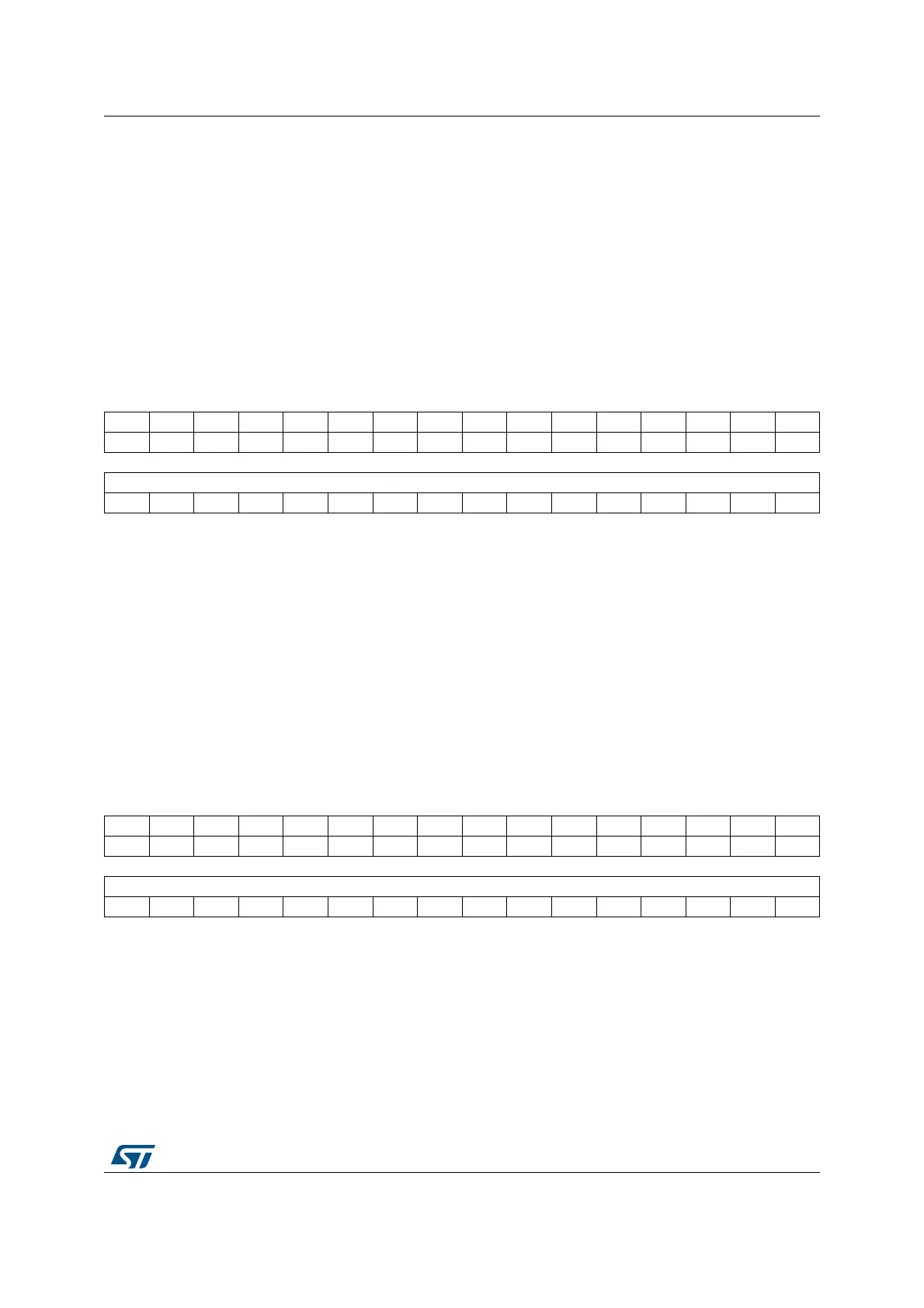

32.7.8 LPTIM counter register (LPTIM_CNT)

Address offset: 0x01C

Reset value: 0x0000 0000

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 CMP[15:0]: Compare value

CMP is the compare value used by the LPTIM.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

ARR[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 ARR[15:0]: Auto reload value

ARR is the autoreload value for the LPTIM.

This value must be strictly greater than the CMP[15:0] value.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

CNT[15:0]

rrrrrrrrrrrrrrrr

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 CNT[15:0]: Counter value

When the LPTIM is running with an asynchronous clock, reading the LPTIM_CNT register may

return unreliable values. So in this case it is necessary to perform two consecutive read accesses

and verify that the two returned values are identical.

It should be noted that for a reliable LPTIM_CNT register read access, two consecutive read

accesses must be performed and compared. A read access can be considered reliable when the

values of the two consecutive read accesses are equal.

Loading...

Loading...