RM0440 Rev 4 1831/2126

RM0440 Serial audio interface (SAI)

1858

40.5.2 SAI configuration register 1 (SAI_BCR1)

Address offset: 0x024

Reset value: 0x0000 0040

Bits 7:5 DS[2:0]: Data size

These bits are set and cleared by software. These bits are ignored when the SPDIF protocols are

selected (bit PRTCFG[1:0]), because the frame and the data size are fixed in such case. When the

companding mode is selected through COMP[1:0] bits, DS[1:0] are ignored since the data size is

fixed to 8 bits by the algorithm.

These bits must be configured when the audio block is disabled.

000: Reserved

001: Reserved

010: 8 bits

011: 10 bits

100: 16 bits

101: 20 bits

110: 24 bits

111: 32 bits

Bit 4 Reserved, must be kept at reset value.

Bits 3:2 PRTCFG[1:0]: Protocol configuration

These bits are set and cleared by software. These bits have to be configured when the audio block is

disabled.

00: Free protocol. Free protocol allows to use the powerful configuration of the audio block to

address a specific audio protocol (such as I2S, LSB/MSB justified, TDM, PCM/DSP...) by setting

most of the configuration register bits as well as frame configuration register.

01: SPDIF protocol

10: AC’97 protocol

11: Reserved

Bits 1:0 MODE[1:0]: SAIx audio block mode

These bits are set and cleared by software. They must be configured when SAIx audio block is

disabled.

00: Master transmitter

01: Master receiver

10: Slave transmitter

11: Slave receiver

Note: When the audio block is configured in SPDIF mode, the master transmitter mode is forced

(MODE[1:0] = 00).

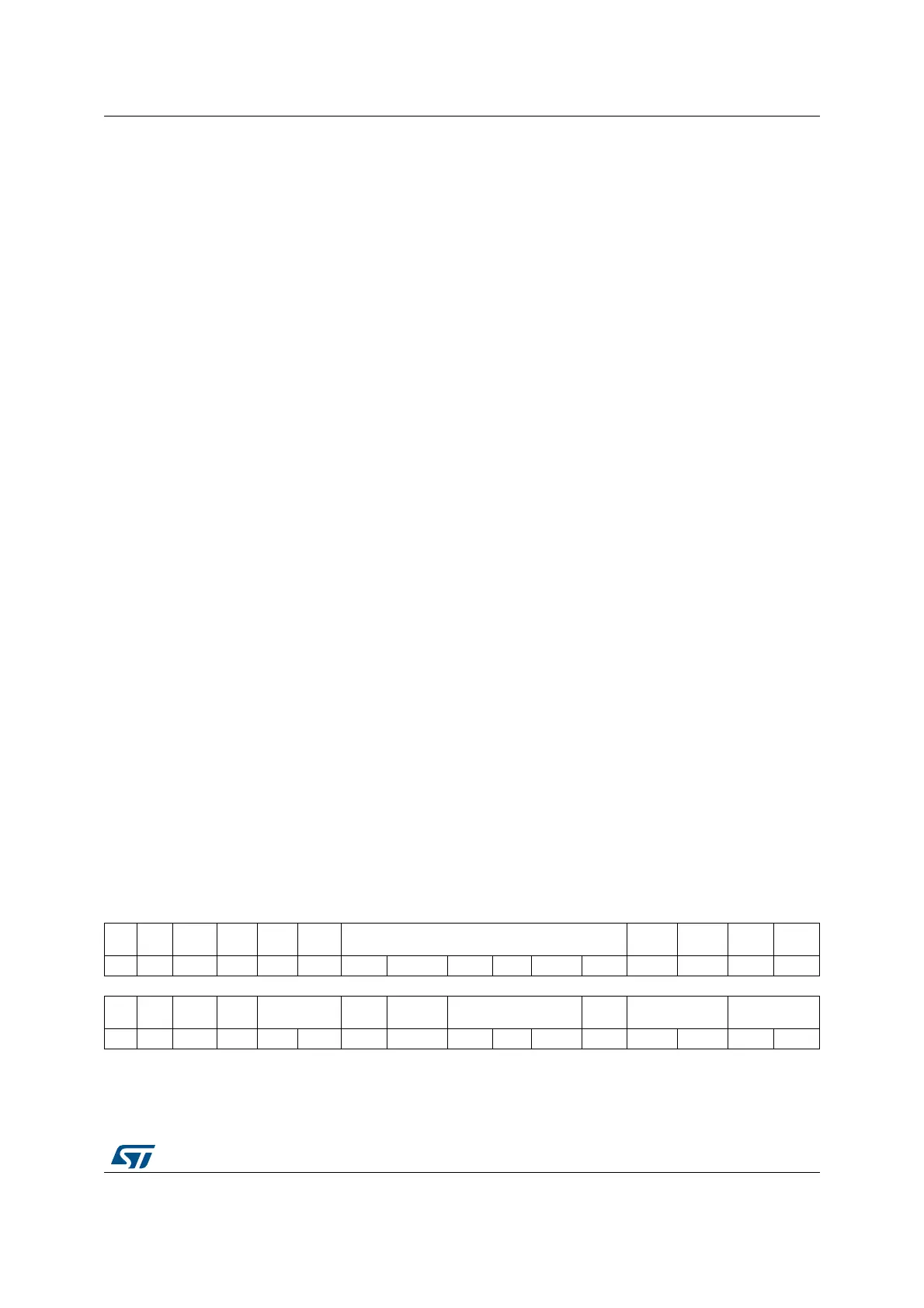

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res.

MCK

EN

OSR MCKDIV[5:0] NODIV Res. DMAEN SAIEN

rw rw rw rw rw rw rw rw rw rw rw

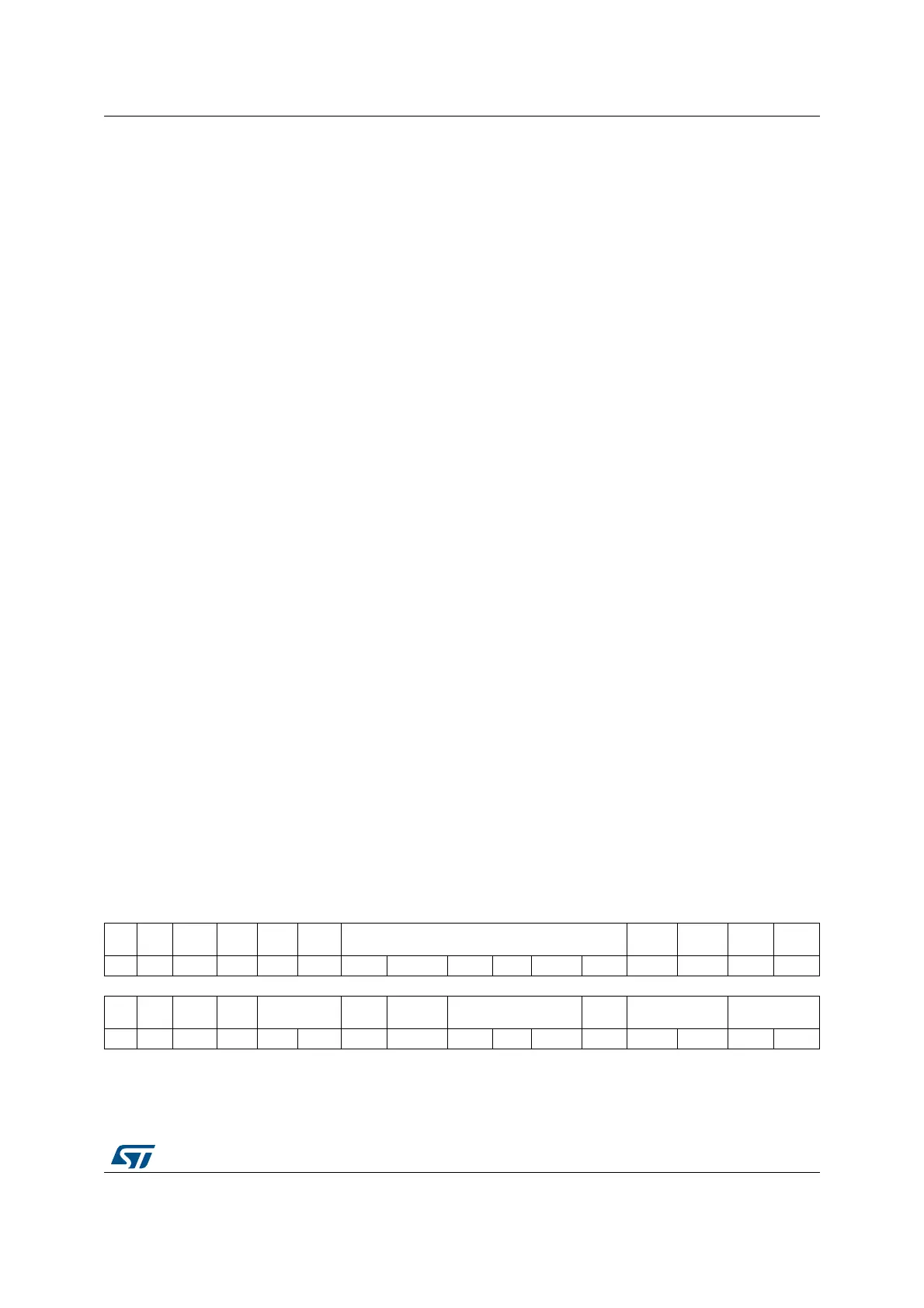

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res.

OUTD

RIV

MONO SYNCEN[1:0] CKSTR LSBFIRST DS[2:0] Res. PRTCFG[1:0] MODE[1:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...