RM0440 Rev 4 451/2126

RM0440 Extended interrupts and events controller (EXTI)

460

15.5 EXTI registers

Refer to Section 1.2 on page 72 for a list of abbreviations used in register descriptions.

The peripheral registers have to be accessed by words (32-bit).

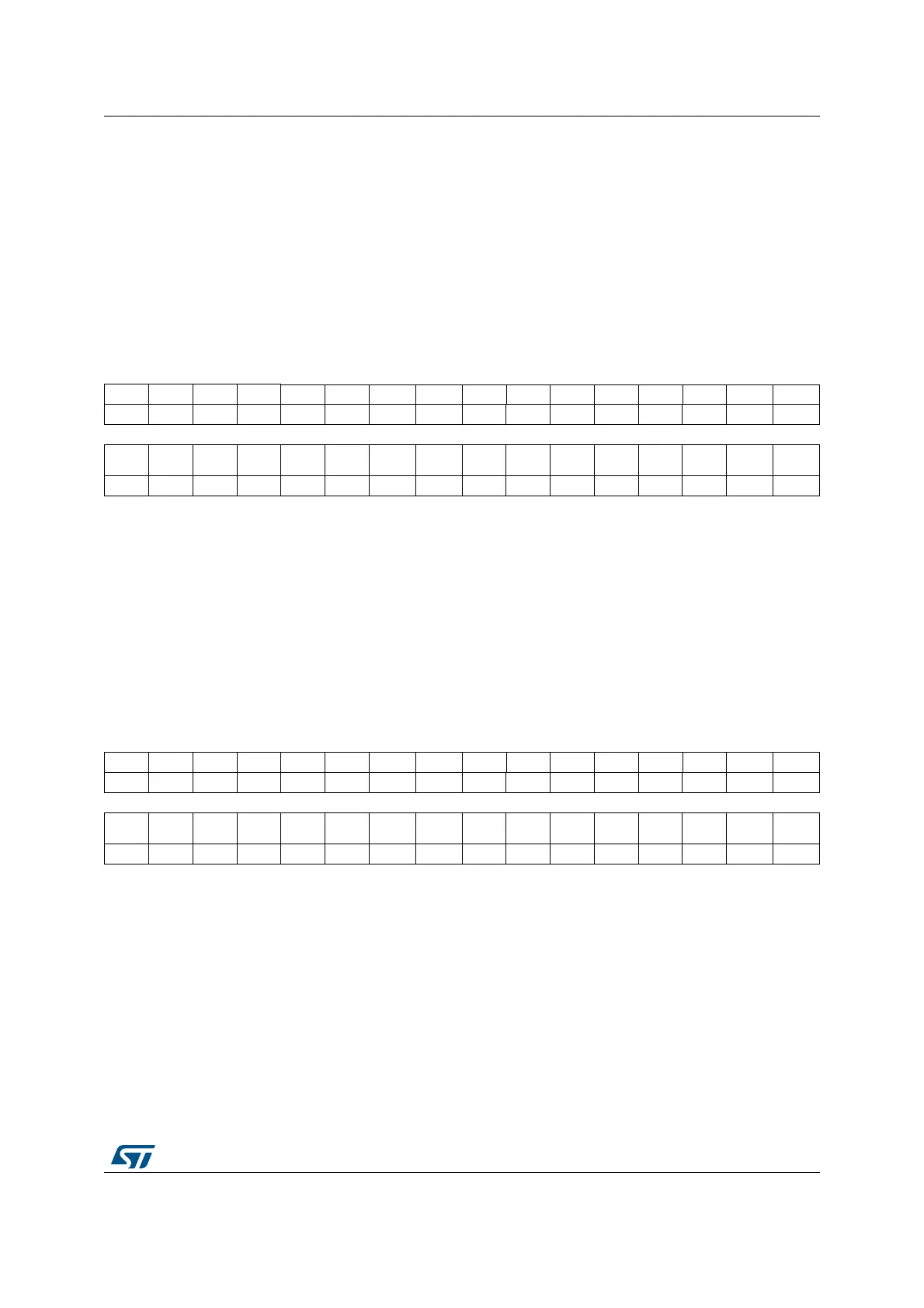

15.5.1 Interrupt mask register 1 (EXTI_IMR1)

Address offset: 0x00

Reset value: Direct lines are set to '1', others lines are set to '0'. See Table 98: EXTI lines

connections.

Note: The reset value for the direct lines is set to ‘1’ in order to enable the interrupt by default.

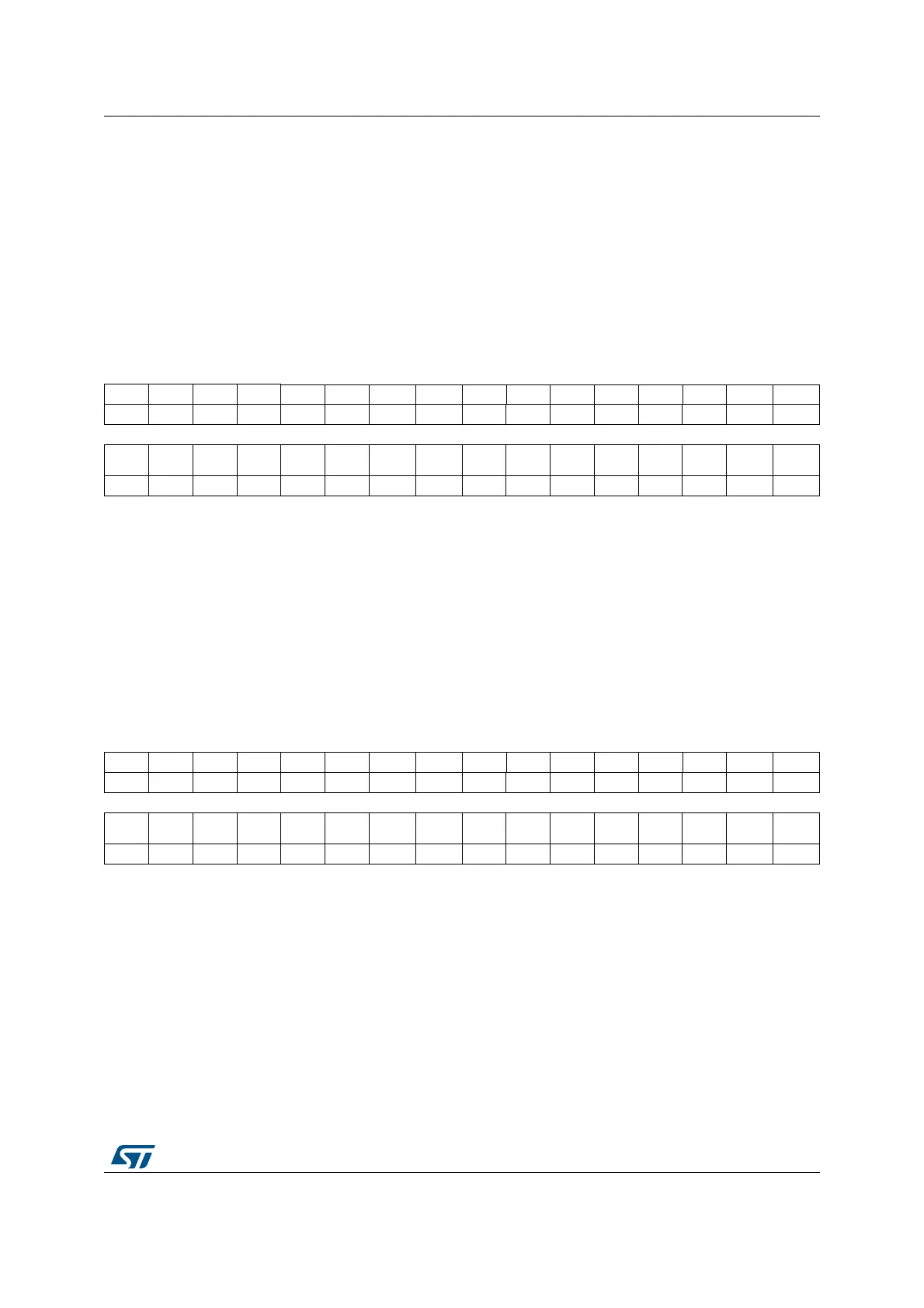

15.5.2 Event mask register 1 (EXTI_EMR1)

Address offset: 0x04

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

IM31 IM30 IM29 IM28 IM27 IM26 IM25 IM24 IM23 IM22 IM21 IM20 IM19 IM18 IM17 IM16

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

IM15 IM14 IM13 IM12 IM11 IM10 IM9 IM8 IM7 IM6 IM5 IM4 IM3 IM2 IM1 IM0

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 IMx: Interrupt Mask on line x (x = 31 to 0)

0: Interrupt request from Line x is masked

1: Interrupt request from Line x is not masked

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

EM31 EM30 .EM29 EM28 EM27 EM26 EM25 EM24 EM23 EM22 EM21 EM20 EM19 EM18 EM17 EM16

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

EM15 EM14 EM13 EM12 EM11 EM10 EM9 EM8 EM7 EM6 EM5 EM4 EM3 EM2 EM1 EM0

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 EMx: Event mask on line x (x = 31 to 0)

0: Event request from line x is masked

1: Event request from line x is not masked

Loading...

Loading...