RM0440 Rev 4 453/2126

RM0440 Extended interrupts and events controller (EXTI)

460

Note: The configurable wakeup lines are edge-triggered. No glitch must be generated on these

lines. If a falling edge on a configurable interrupt line occurs during a write operation to the

EXTI_FTSR register, the pending bit is not set.

Rising and falling edge triggers can be set for the same interrupt line. In this case, both

generate a trigger condition.

15.5.5 Software interrupt event register 1 (EXTI_SWIER1)

Address offset: 0x10

Reset value: 0x0000 0000

Bits 31:29 FTx: Falling trigger event configuration bit of line x (x = 31 to 29)

0: Falling trigger disabled (for Event and Interrupt) for input line

1: Falling trigger enabled (for Event and Interrupt) for input line

Bits 28:23 Reserved, must be kept at reset value.

Bits 22:19 FTx: Falling trigger event configuration bit of line x (x = 22 to 19)

0: Falling trigger disabled (for Event and Interrupt) for input line

1: Falling trigger enabled (for Event and Interrupt) for input line

Bit 18 Reserved, must be kept at reset value.

Bits 17:0 FTx: Falling trigger event configuration bit of line x (x = 17 to 0)

0: Falling trigger disabled (for Event and Interrupt) for input line

1: Falling trigger enabled (for Event and Interrupt) for input line

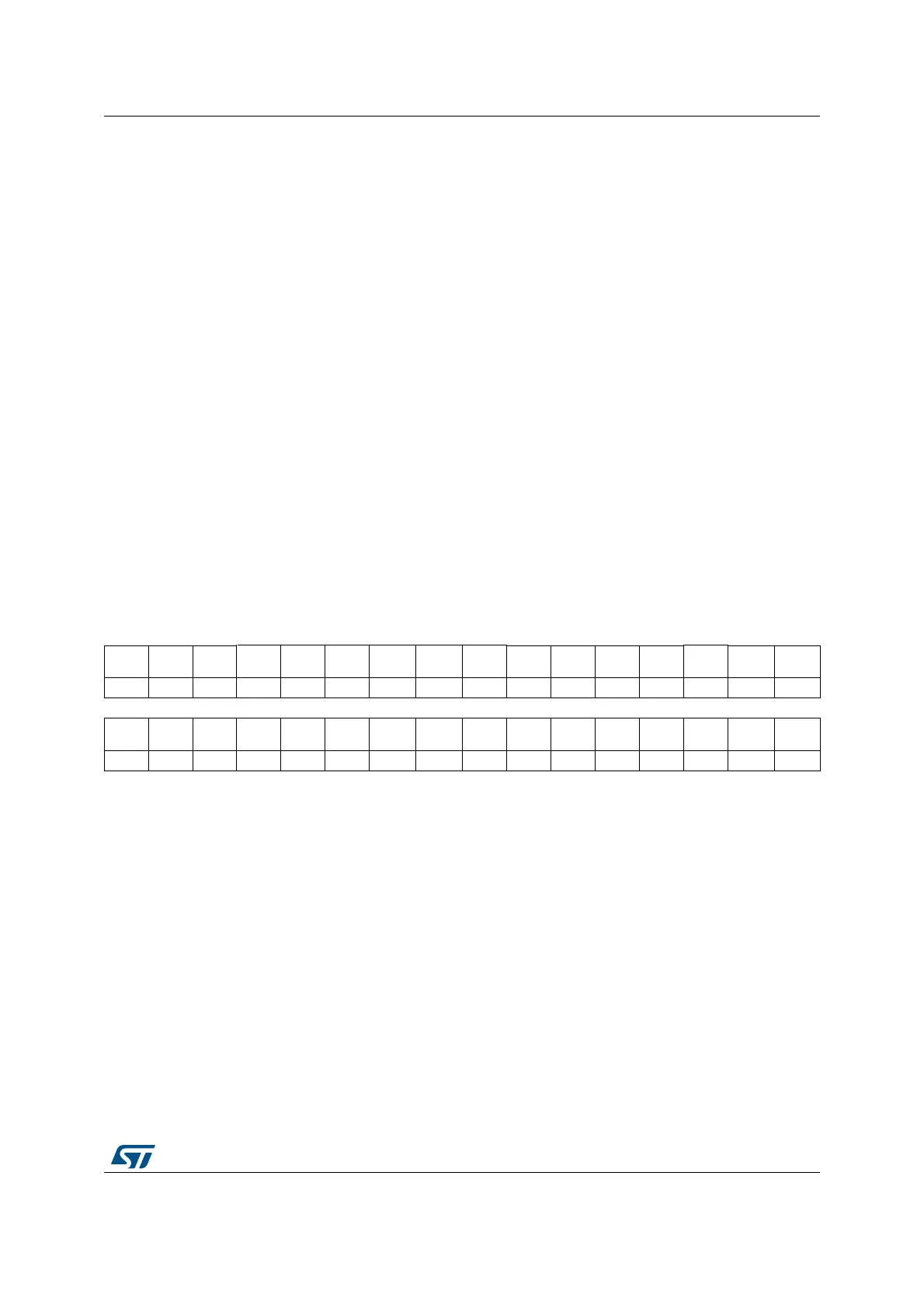

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

SWI

31

SWI

30

SWI

29

Res. Res. Res. Res. Res. Res.

SWI

22

SWI

21

SWI

20

SWI

19

Res.

SWI

17

SWI

16

rw rw rw rw rw rw rw rw rw

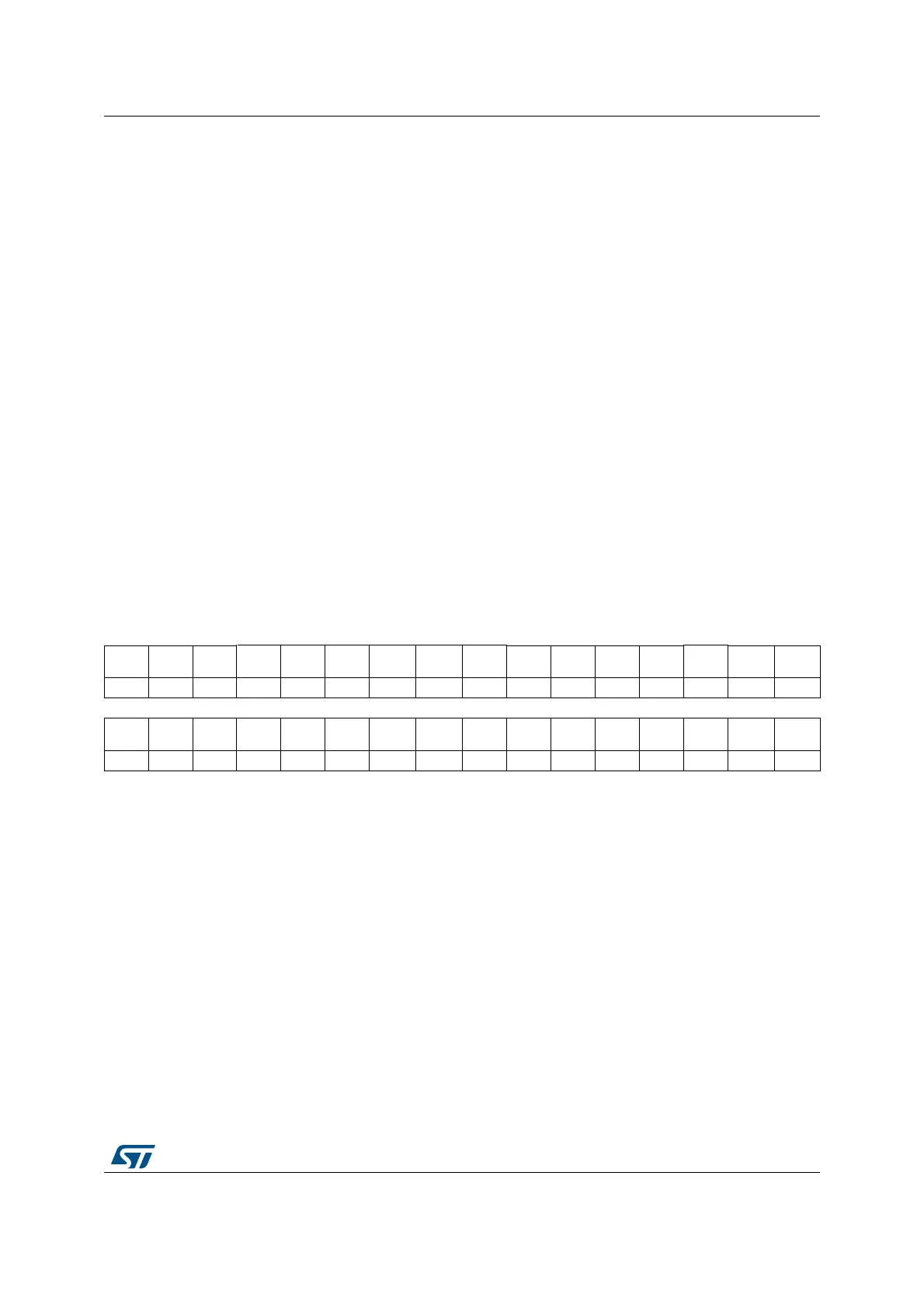

1514131211109 8 765432 1 0

SWI

15

SWI

14

SWI

13

SWI

12

SWI

11

SWI

10

SWI

9

SWI

8

SWI

7

SWI

6

SWI

5

SWI

4

SWI

3

SWI

2

SWI

1

SWI

0

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:29 SWIx: Software interrupt on line x (x = 31 o 29)

If the interrupt is enabled on this line in the EXTI_IMR, writing a '1' to this bit

when it is at '0' sets the corresponding pending bit in EXTI_PR resulting in an

interrupt request generation.

This bit is cleared by clearing the corresponding bit in the EXTI_PR register (by

writing a ‘1’ into the bit).

Bits 28:23 Reserved, must be kept at reset value.

Loading...

Loading...