RM0440 Rev 4 459/2126

RM0440 Extended interrupts and events controller (EXTI)

460

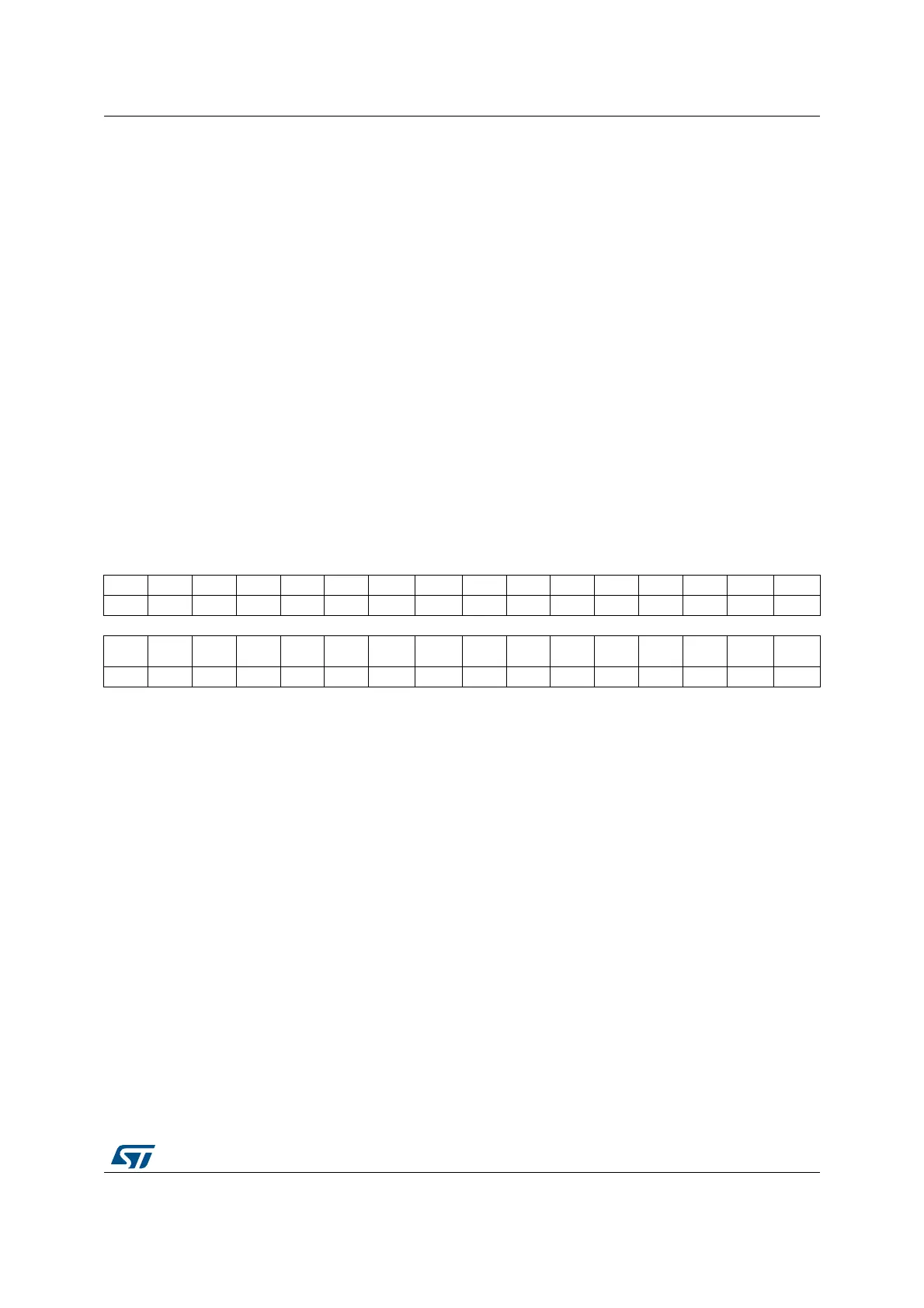

15.5.12 Pending register 2 (EXTI_PR2)

Address offset: 0x34

Reset value: undefined

Bits 31:10 Reserved, must be kept at reset value.

Bits 9:8 SWIx: Software interrupt on line x (x = 40 to 41)

If the interrupt is enabled on this line in EXTI_IMR, writing a '1' to this bit when it

is at '0' sets the corresponding pending bit of EXTI_PR resulting in an interrupt

request generation.

This bit is cleared by clearing the corresponding bit of EXTI_PR (by writing a ‘1’

to the bit).

Bits 7:2 Reserved, must be kept at reset value.

Bits 1:0 SWIx: Software interrupt on line x (x = 32 to 33)

If the interrupt is enabled on this line in EXTI_IMR, writing a '1' to this bit when it

is at '0' sets the corresponding pending bit of EXTI_PR resulting in an interrupt

request generation.

This bit is cleared by clearing the corresponding bit of EXTI_PR (by writing a ‘1’

to the bit).

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109 8 765432 1 0

Res. Res. Res. Res. Res. Res. PIF41 PIF40 Res. Res. Res. Res. Res. Res. PIF33 PIF32

rc_w1 rc_w1 rc_w1 rc_w1

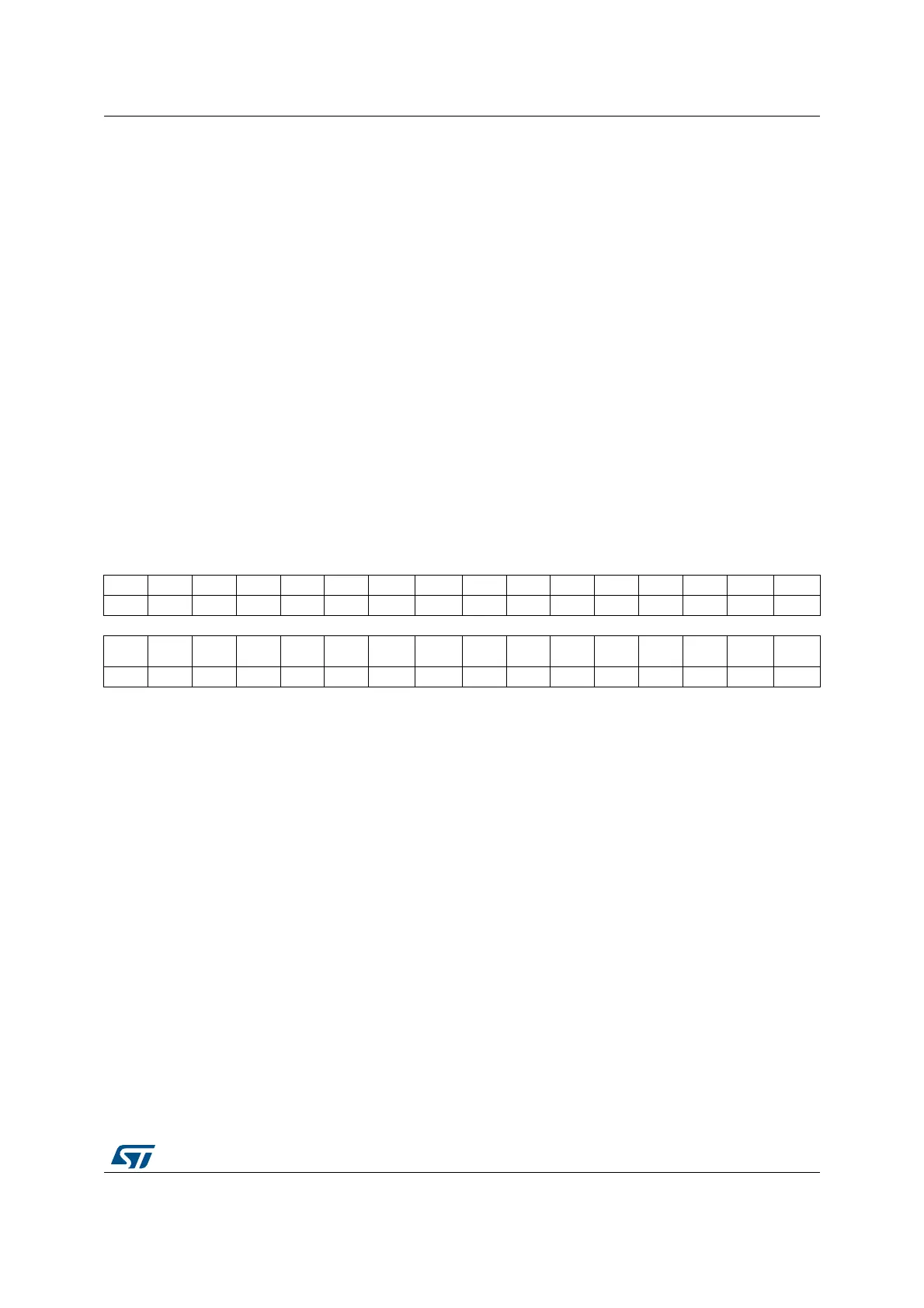

Bits 31:10 Reserved, must be kept at reset value.

Bits 9:8 PIFx: Pending interrupt flag on line x (x = 40 to 41)

0: No trigger request occurred

1: Selected trigger request occurred

This bit is set when the selected edge event arrives on the interrupt line. This bit

is cleared by writing a ‘1’ into the bit.

Bits 7:2 Reserved, must be kept at reset value.

Bits 1:0 PIFx: Pending interrupt flag on line x (x = 32 to 33)

0: No trigger request occurred

1: Selected trigger request occurred

This bit is set when the selected edge event arrives on the interrupt line. This bit

is cleared by writing a ‘1’ into the bit.

Loading...

Loading...