Filter math accelerator (FMAC) RM0440

506/2126 RM0440 Rev 4

18.4 FMAC registers

18.4.1 FMAC X1 buffer configuration register (FMAC_X1BUFCFG)

Address offset: 0x00

Reset value: 0x0000 0000

This register can only be modified if START = 0 in the FMAC_PARAM register.

18.4.2 FMAC X2 buffer configuration register (FMAC_X2BUFCFG)

Address offset: 0x04

Reset value: 0x0000 0000

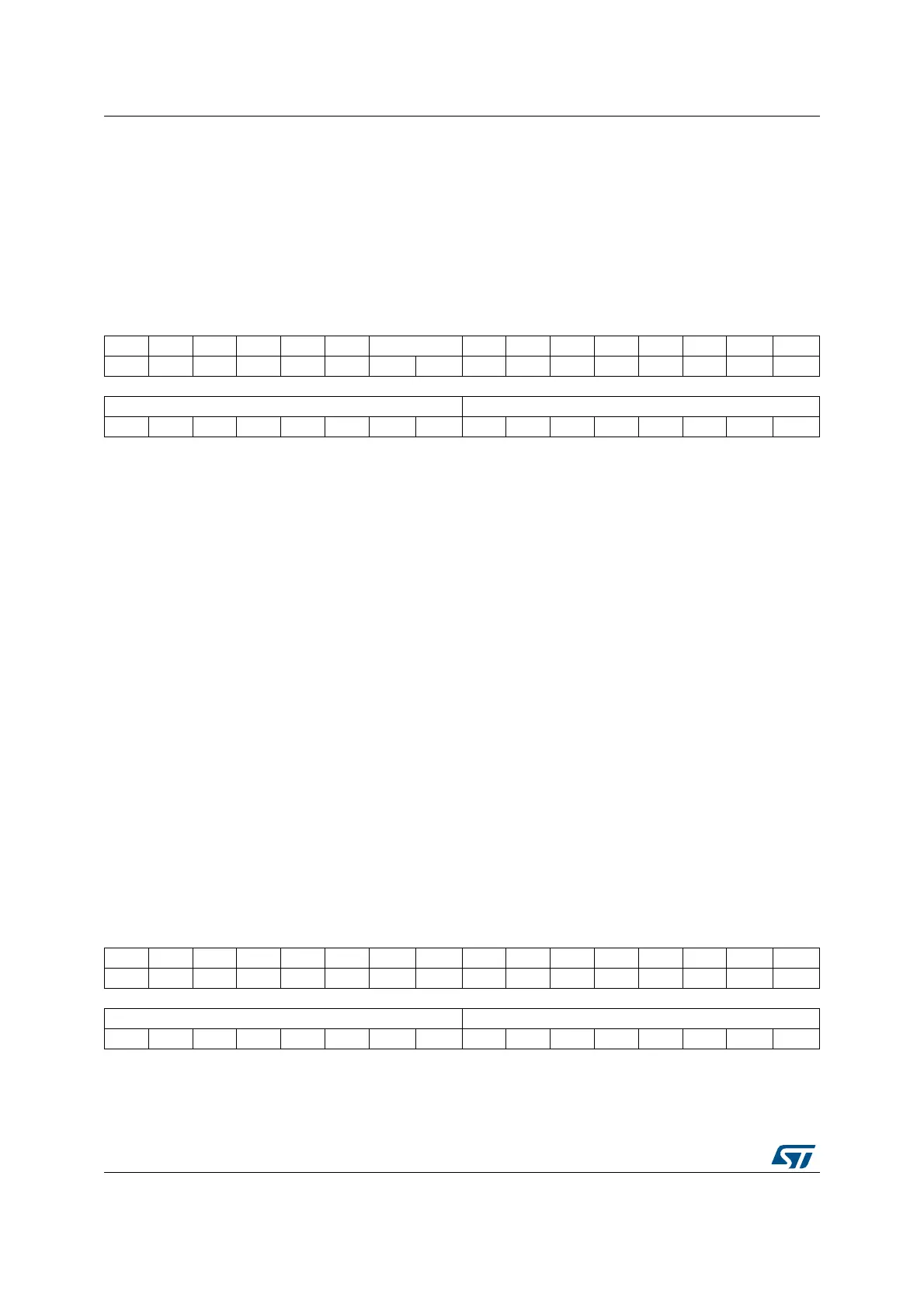

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. FULL_WM[1:0] Res. Res. Res. Res. Res. Res. Res. Res.

rw rw

1514131211109 8 765432 1 0

X1_BUF_SIZE[7:0] X1_BASE[7:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:26 Reserved, must be kept at reset value.

Bits 25:24 FULL_WM[1:0]: Watermark for buffer full flag

Defines the threshold for setting the X1 buffer full flag when operating in circular mode. The

flag is set if the number of free spaces in the buffer is less than 2

FULL_WM

.

0: Threshold = 1

1: Threshold = 2

2: Threshold = 4

3: Threshold = 8

Setting a threshold greater than 1 allows several data to be transferred into the buffer under

one interrupt.

Threshold should be set to 1 if DMA write requests are enabled (DMAWEN = 1 in FMAC_CR

register).

Bits 23:16 Reserved, must be kept at reset value.

Bits 15:8 X1_BUF_SIZE[7:0]: Allocated size of X1 buffer in 16-bit words

The minimum buffer size is the number of feed-forward taps in the filter (+ the watermark

threshold - 1).

Bits 7:0 X1_BASE[7:0]: Base address of X1 buffer

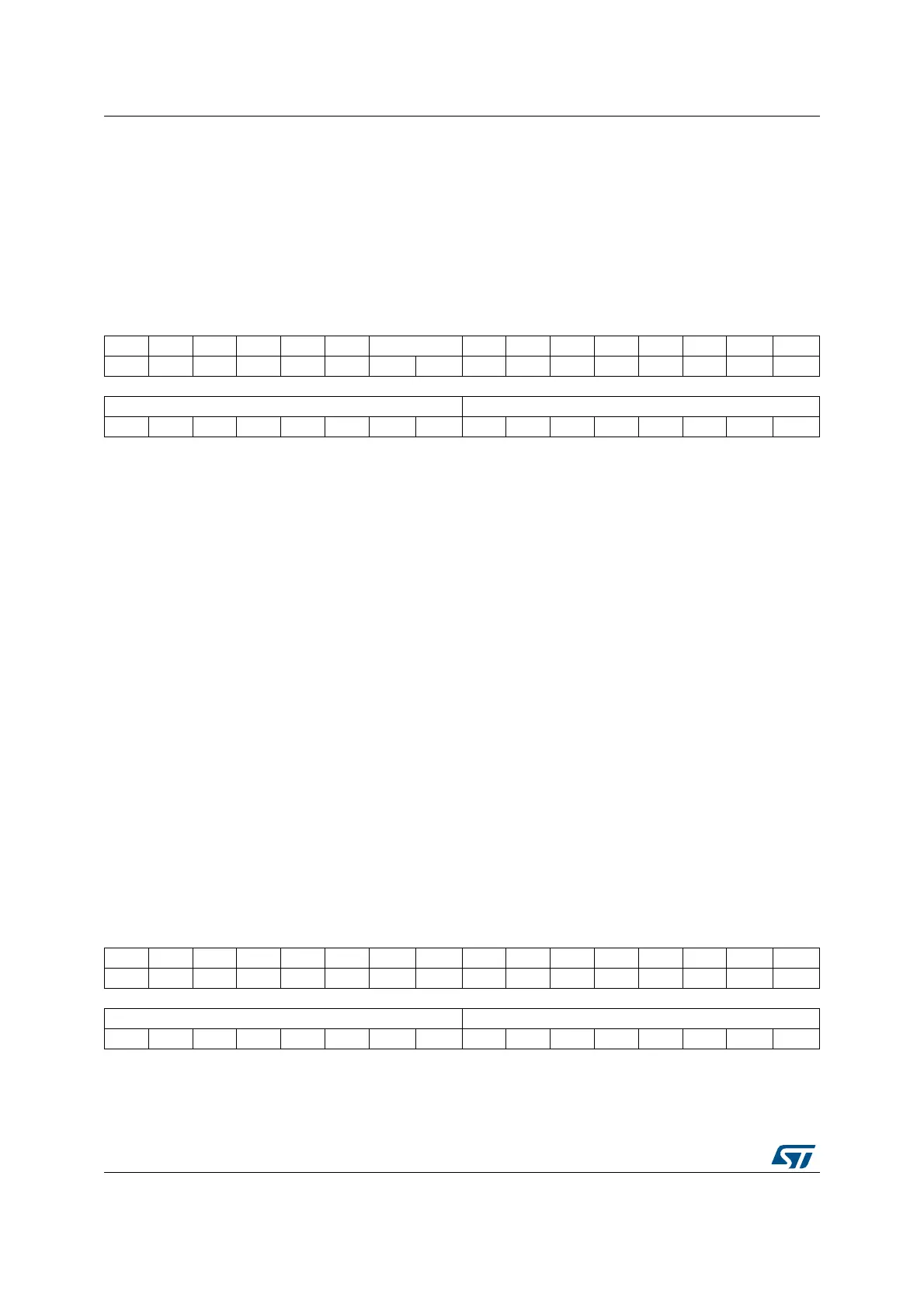

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109 8 765432 1 0

X2_BUF_SIZE[7:0] X2_BASE[7:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...