RM0440 Rev 4 705/2126

RM0440 Analog-to-digital converters (ADC)

724

Note: Some channels are not connected physically and must not be selected for conversion.

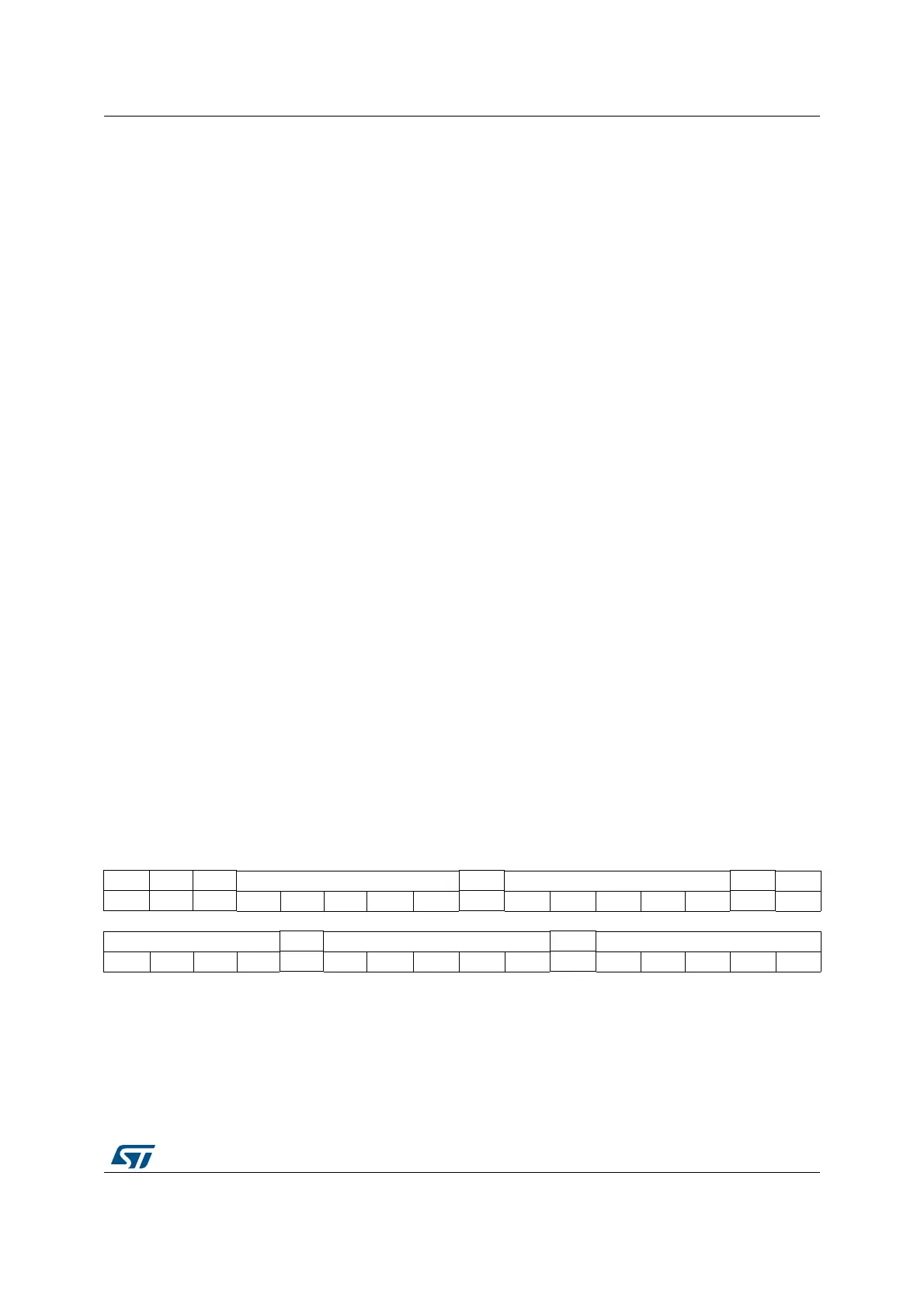

21.6.12 ADC regular sequence register 2 (ADC_SQR2)

Address offset: 0x34

Reset value: 0x0000 0000

Bits 22:18 SQ3[4:0]: 3rd conversion in regular sequence

These bits are written by software with the channel number (0 to 18) assigned as the 3rd in

the regular conversion sequence.

Note: The software is allowed to write these bits only when ADSTART=0 (which ensures that

no regular conversion is ongoing).

Bit 17 Reserved, must be kept at reset value.

Bits 16:12 SQ2[4:0]: 2nd conversion in regular sequence

These bits are written by software with the channel number (0 to 18) assigned as the 2nd in

the regular conversion sequence.

Note: The software is allowed to write these bits only when ADSTART=0 (which ensures that

no regular conversion is ongoing).

Bit 11 Reserved, must be kept at reset value.

Bits 10:6 SQ1[4:0]: 1st conversion in regular sequence

These bits are written by software with the channel number (0 to 18) assigned as the 1st in

the regular conversion sequence.

Note: The software is allowed to write these bits only when ADSTART=0 (which ensures that

no regular conversion is ongoing).

Bits 5:4 Reserved, must be kept at reset value.

Bits 3:0 L[3:0]: Regular channel sequence length

These bits are written by software to define the total number of conversions in the regular

channel conversion sequence.

0000: 1 conversion

0001: 2 conversions

...

1111: 16 conversions

Note: The software is allowed to write these bits only when ADSTART=0 (which ensures that

no regular conversion is ongoing).

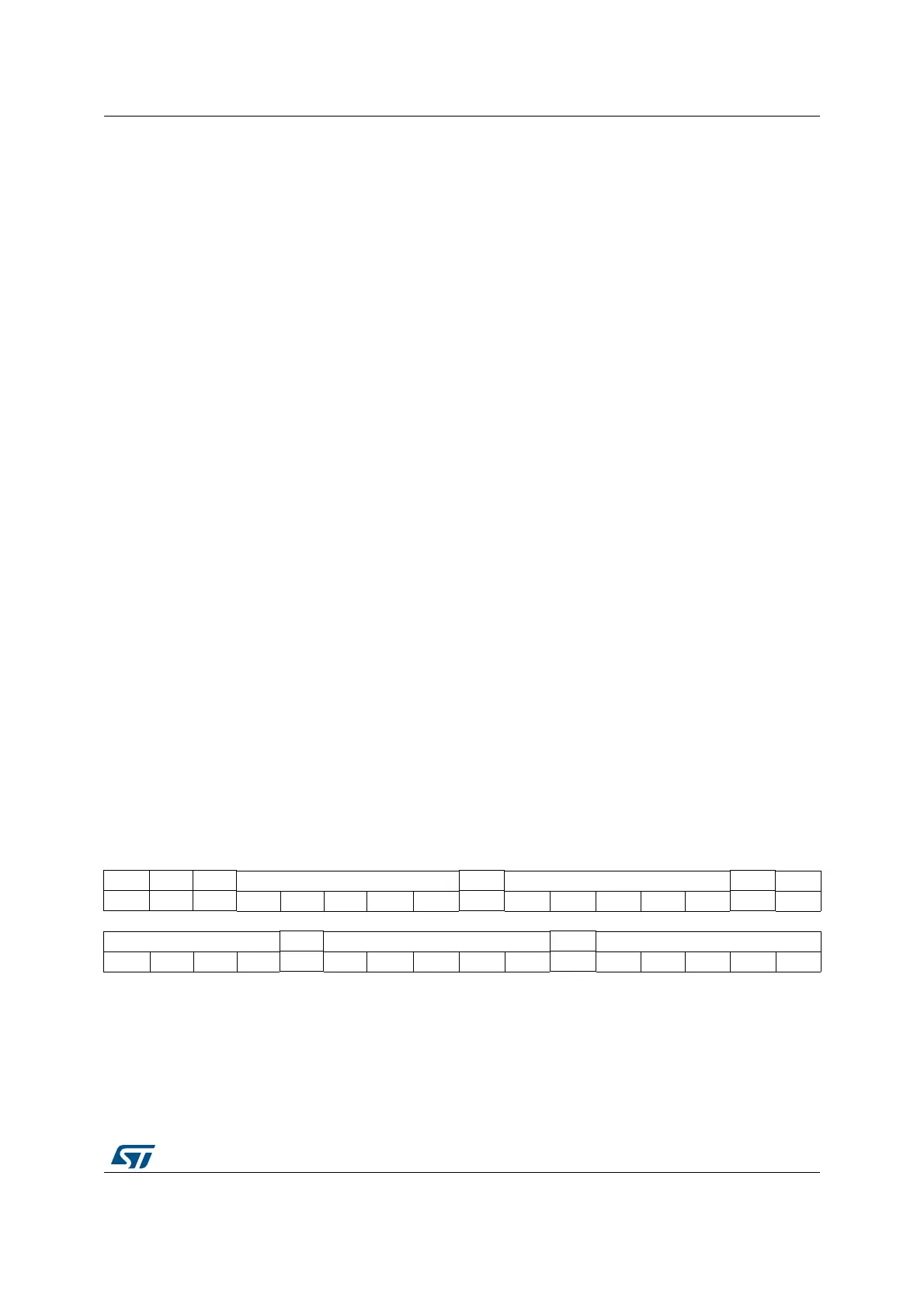

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. SQ9[4:0] Res. SQ8[4:0] Res. SQ7[4]

rw rw rw rw rw rw rw rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SQ7[3:0] Res. SQ6[4:0] Res. SQ5[4:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...