RM0440 Rev 4 1325/2126

RM0440 General-purpose timers (TIM2/TIM3/TIM4/TIM5)

1343

Note: The state of the external IO pins connected to the standard tim_ocx channels depends only

on the GPIO registers when CCxE=0.

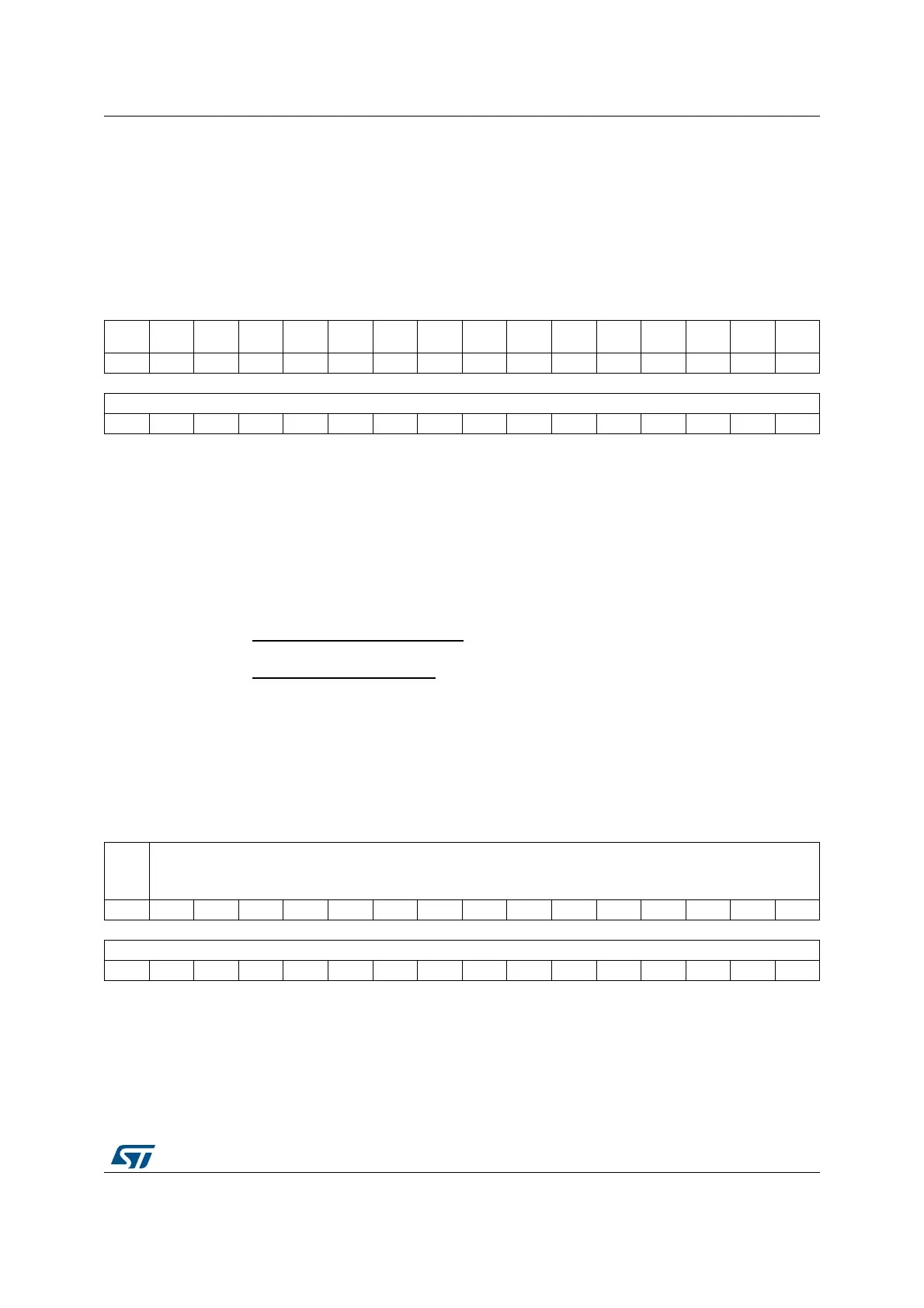

29.5.12 TIMx counter (TIMx_CNT)(x = 3, 4)

Address offset: 0x024

Reset value: 0x0000 0000

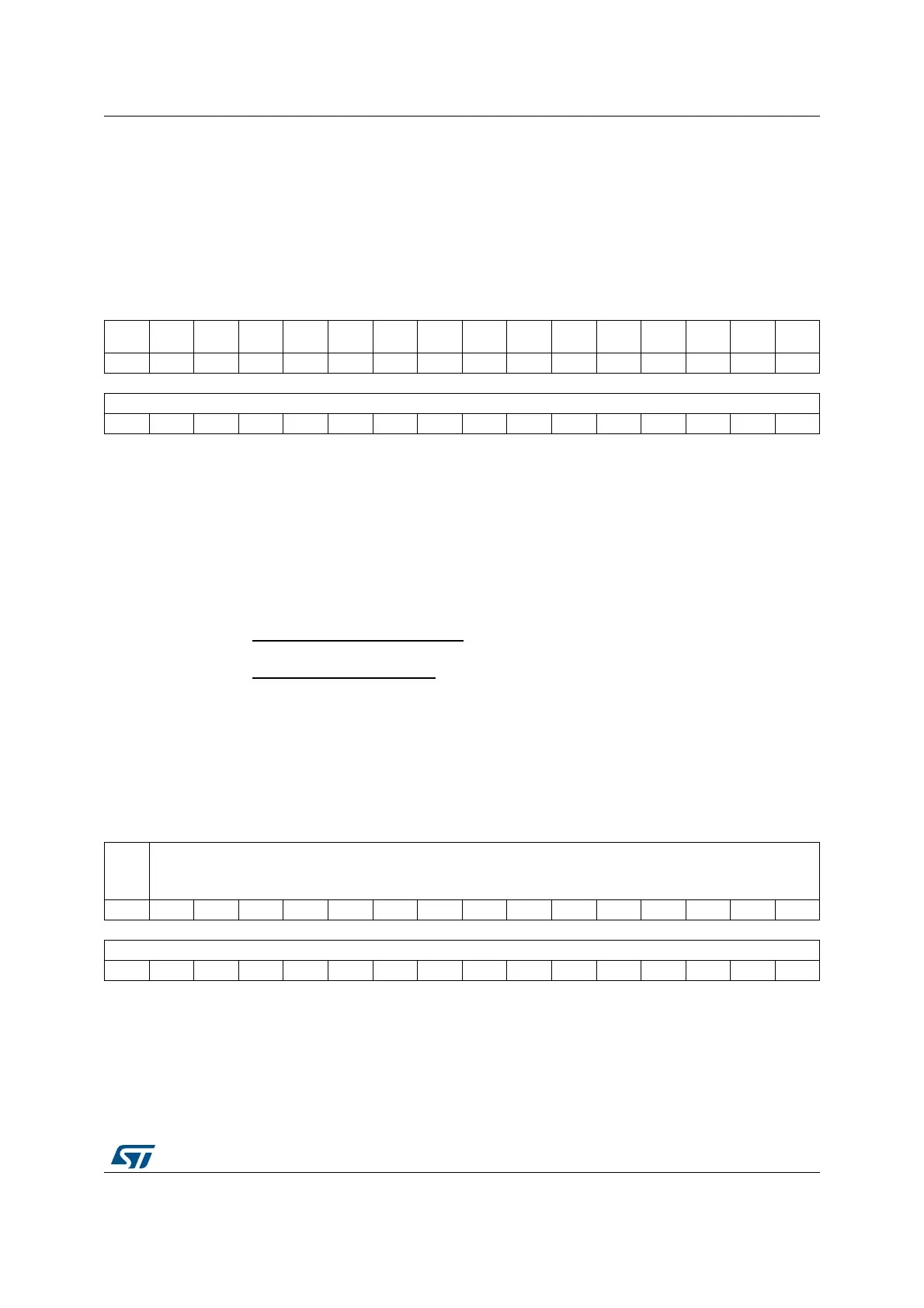

29.5.13 TIMx counter (TIMx_CNT)(x = 2, 5)

Address offset: 0x024

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

UIF

CPY

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

rw

1514131211109876543210

CNT[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bit 31 UIFCPY: Value depends on IUFREMAP in TIMx_CR1.

If UIFREMAP = 0

Reserved

If UIFREMAP = 1

UIFCPY: UIF Copy

This bit is a read-only copy of the UIF bit of the TIMx_ISR register

Bits 30:16 Reserved, must be kept at reset value.

Bits 15:0 CNT[15:0]: Counter value‘

Non-dithering mode (DITHEN = 0)

The register holds the counter value.

Dithering mode (DITHEN = 1)

The register holds the non-dithered part in CNT[15:0]. The fractional part is not available.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

CNT

[31]

or UIF

CPY

CNT[30:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

CNT[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...