RM0440 Rev 4 1327/2126

RM0440 General-purpose timers (TIM2/TIM3/TIM4/TIM5)

1343

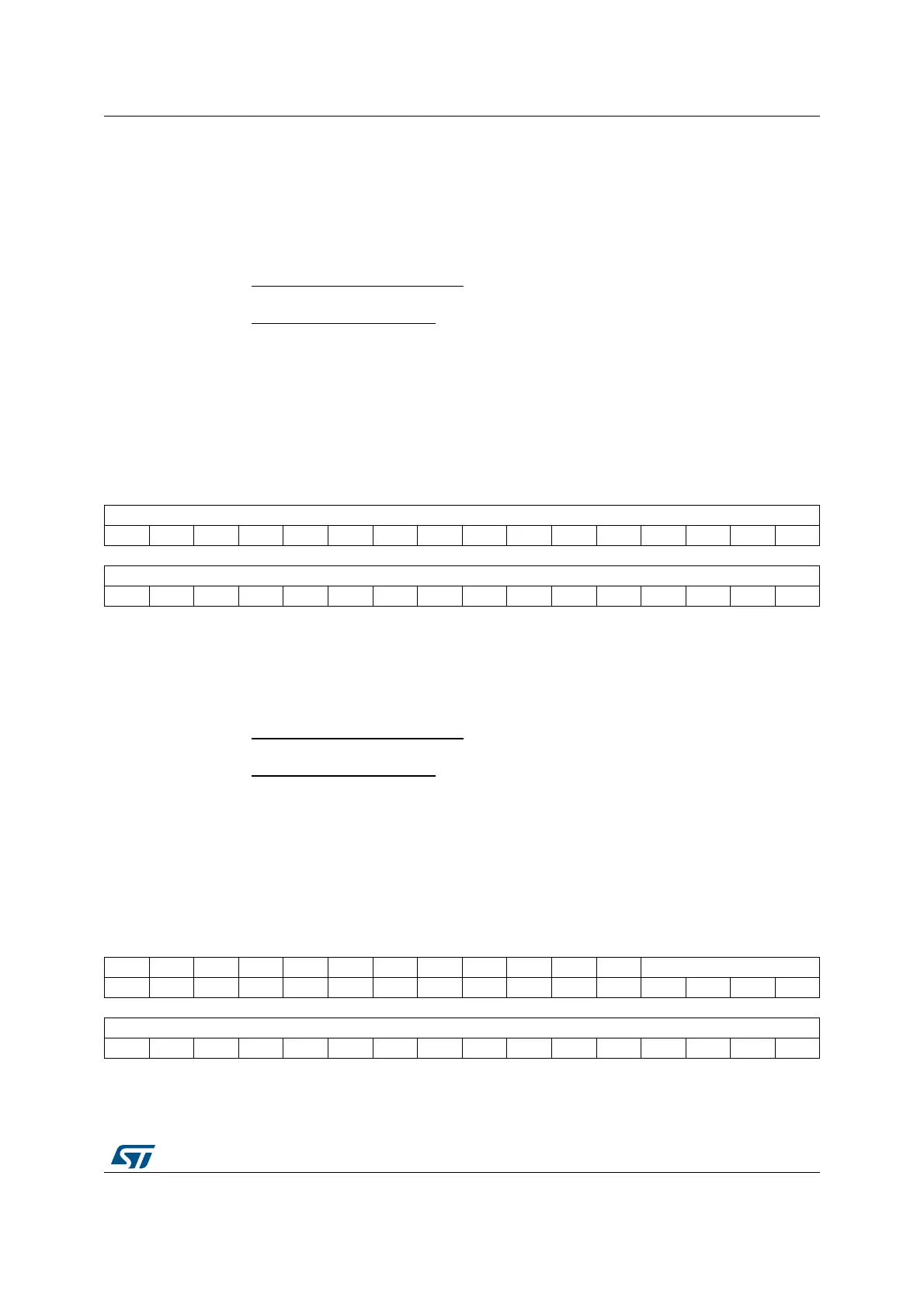

29.5.16 TIMx auto-reload register (TIMx_ARR)(x = 2, 5)

Address offset: 0x02C

Reset value: 0xFFFF FFFF

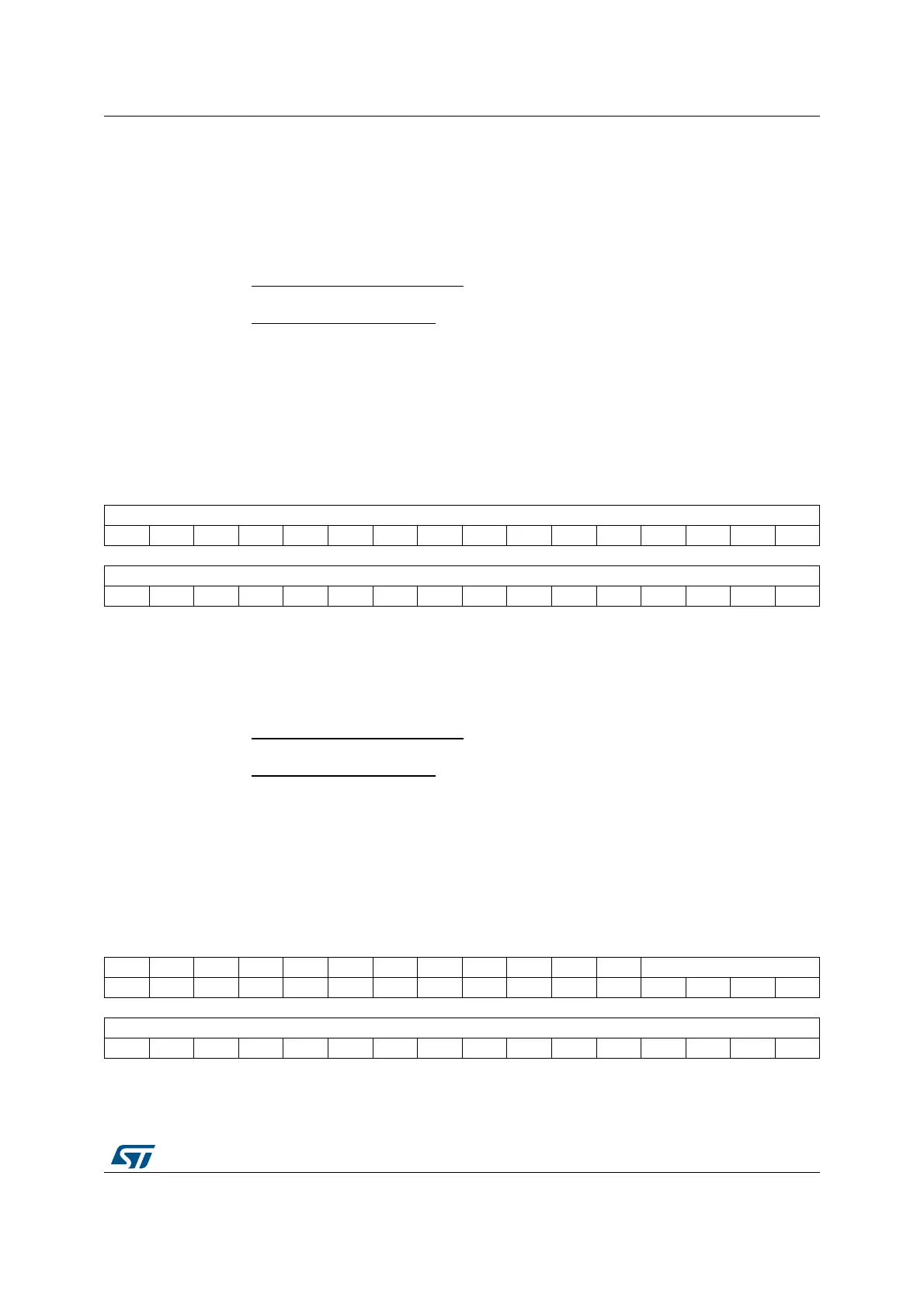

29.5.17 TIMx capture/compare register 1 (TIMx_CCR1)(x = 3, 4)

Address offset: 0x034

Reset value: 0x0000 0000

Bits 31:20 Reserved, must be kept at reset value.

Bits 19:0 ARR[19:0]: Low Auto-reload value

ARR is the value to be loaded in the actual auto-reload register.

Refer to the Section 29.4.3: Time-base unit on page 1234 for more details about ARR

update and behavior.

The counter is blocked while the auto-reload value is null.

Non-dithering mode (DITHEN = 0)

The register holds the auto-reload value.

Dithering mode (DITHEN = 1)

The register holds the integer part in ARR[19:4]. The ARR[3:0] bitfield contains the dithered

part.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

ARR[31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

ARR[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 ARR[31:0]: Auto-reload value

ARR is the value to be loaded in the actual auto-reload register.

Refer to the Section 29.4.3: Time-base unit on page 1234 for more details about ARR

update and behavior.

The counter is blocked while the auto-reload value is null.

Non-dithering mode (DITHEN = 0)

The register holds the auto-reload value.

Dithering mode (DITHEN = 1)

The register holds the integer part in ARR[31:4]. The ARR[3:0] bitfield contains the dithered

part.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. CCR1[19:16]

rw rw rw rw

1514131211109876543210

CCR1[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...