General-purpose timers (TIM15/TIM16/TIM17) RM0440

1394/2126 RM0440 Rev 4

30.7.3 TIM15 slave mode control register (TIM15_SMCR)

Address offset: 0x08

Reset value: 0x0000 0000

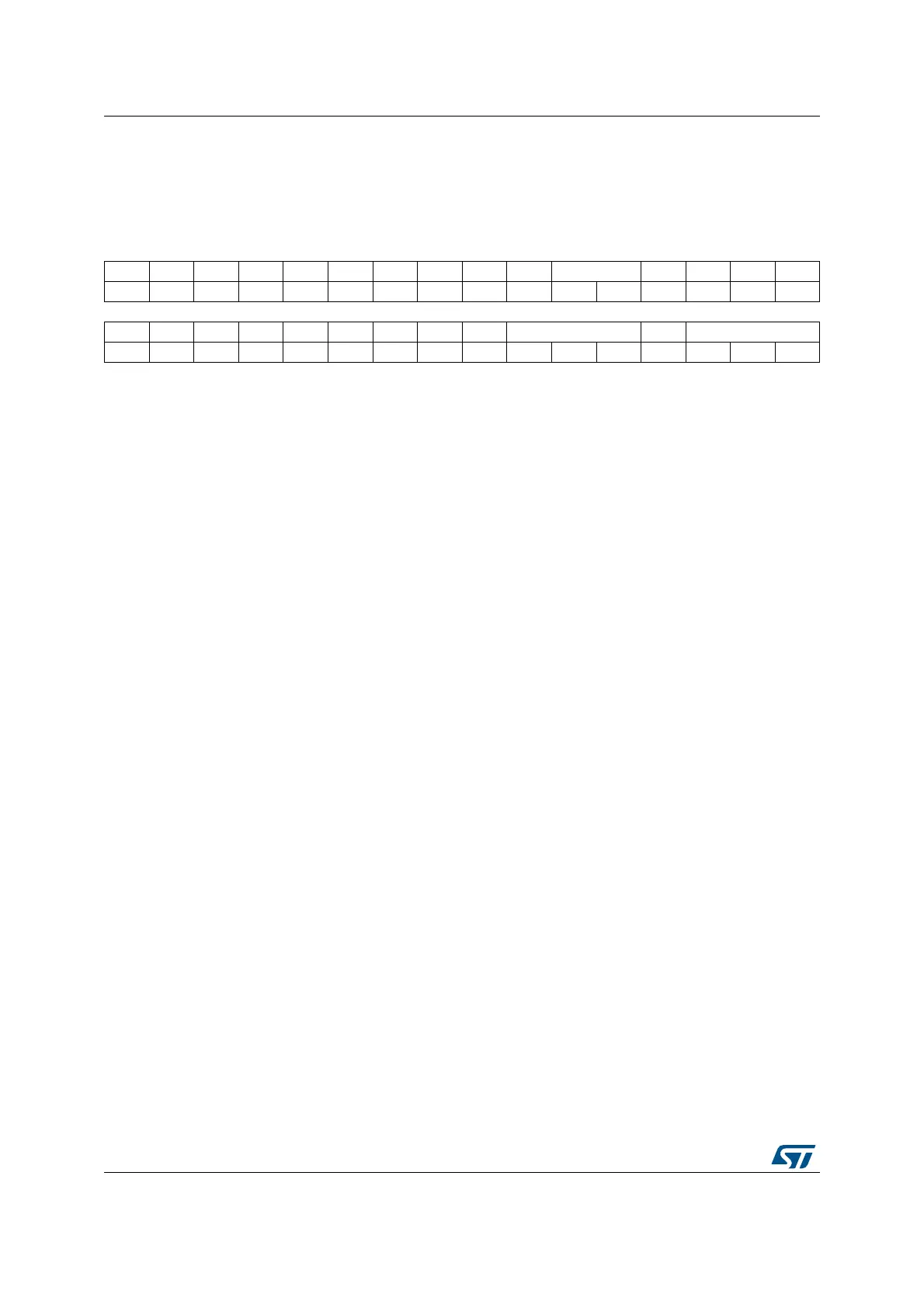

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. TS[4:3] Res. Res. Res. SMS[3]

rw rw rw

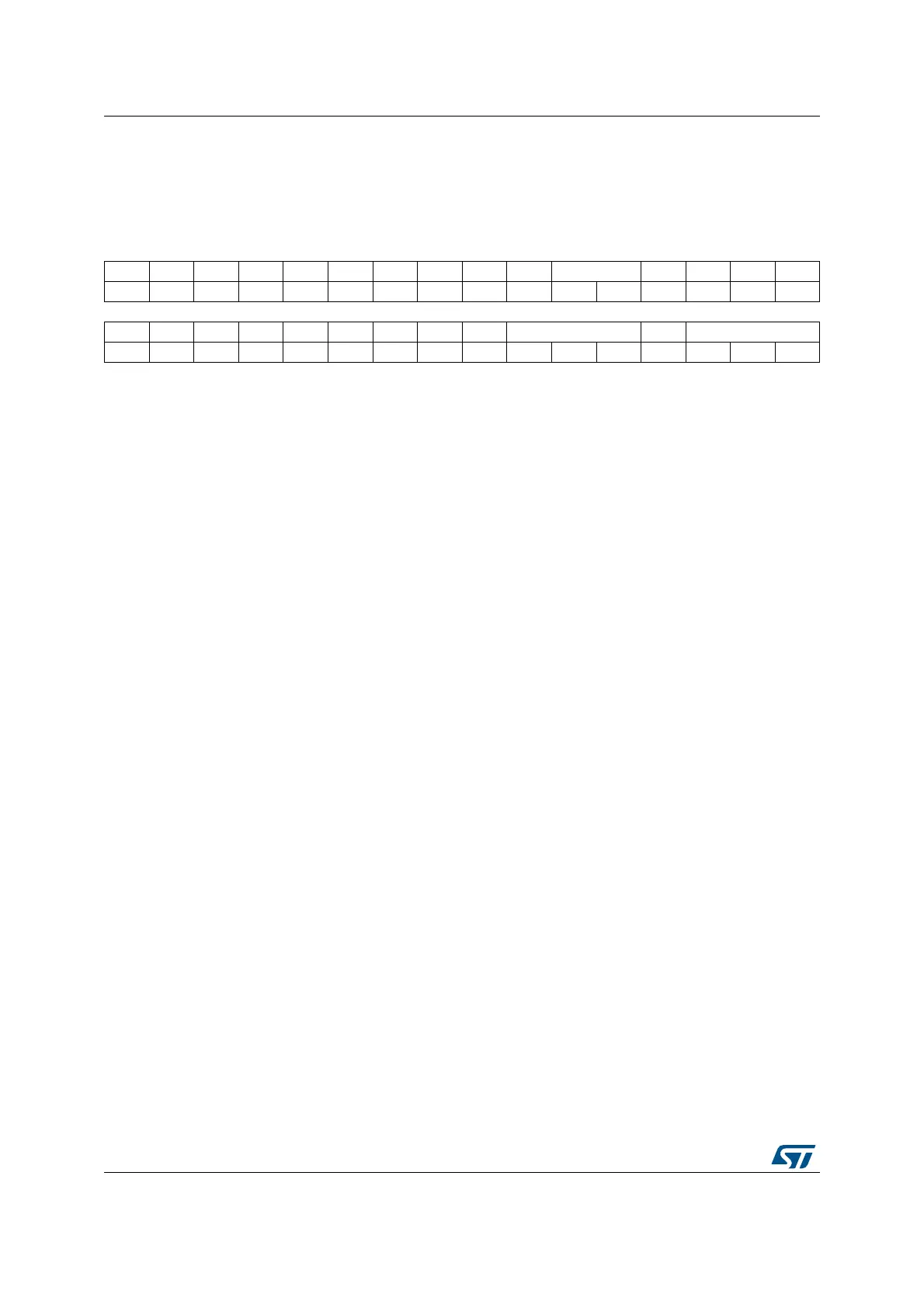

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. MSM TS[2:0] Res. SMS[2:0]

rw rw rw rw rw rw rw

Bits 31:22 Reserved, must be kept at reset value.

Bits 19:17 Reserved, must be kept at reset value.

Bits 15:8 Reserved, must be kept at reset value.

Bit 7 MSM: Master/slave mode

0: No action

1:The effect of an event on the trigger input (tim_trgi) is delayed to allow a perfect

synchronization between the current timer and its slaves (through tim_trgo). It is useful if

we want to synchronize several timers on a single external event.

Bits 21, 20, 6, 5, 4 TS[4:0]: Trigger selection

This bit field selects the trigger input to be used to synchronize the counter.

00000: Internal Trigger 0 (tim_itr0)

00001: Internal Trigger 1 (tim_itr1)

00010: Internal Trigger 2 (tim_itr2)

00011: Internal Trigger 3 (tim_itr3)

00100: tim_ti1 Edge Detector (tim_ti1f_ed)

00101: Filtered Timer Input 1 (tim_ti1fp1)

00110: Filtered Timer Input 2 (tim_ti2fp2)

00111: Reserved

01000: Internal Trigger 4 (tim_itr4)

01001: Internal Trigger 5 (tim_itr5)

01010: Internal Trigger 6 (tim_itr6)

01011: Internal Trigger 7 (tim_itr7)

01100: Internal Trigger 8 (tim_itr8)

01101: Internal Trigger 9 (tim_itr9)

01110: Internal Trigger 10 (tim_itr10)

Others: Reserved

See Section 30.4.2: TIM15/TIM16/TIM17 pins and internal signals for more details on

tim_itrx meaning for each timer.

Note: These bits must be changed only when they are not used (e.g. when SMS=000) to

avoid wrong edge detections at the transition.

Bit 3 Reserved, must be kept at reset value.

Loading...

Loading...