RM0440 Rev 4 1395/2126

RM0440 General-purpose timers (TIM15/TIM16/TIM17)

1445

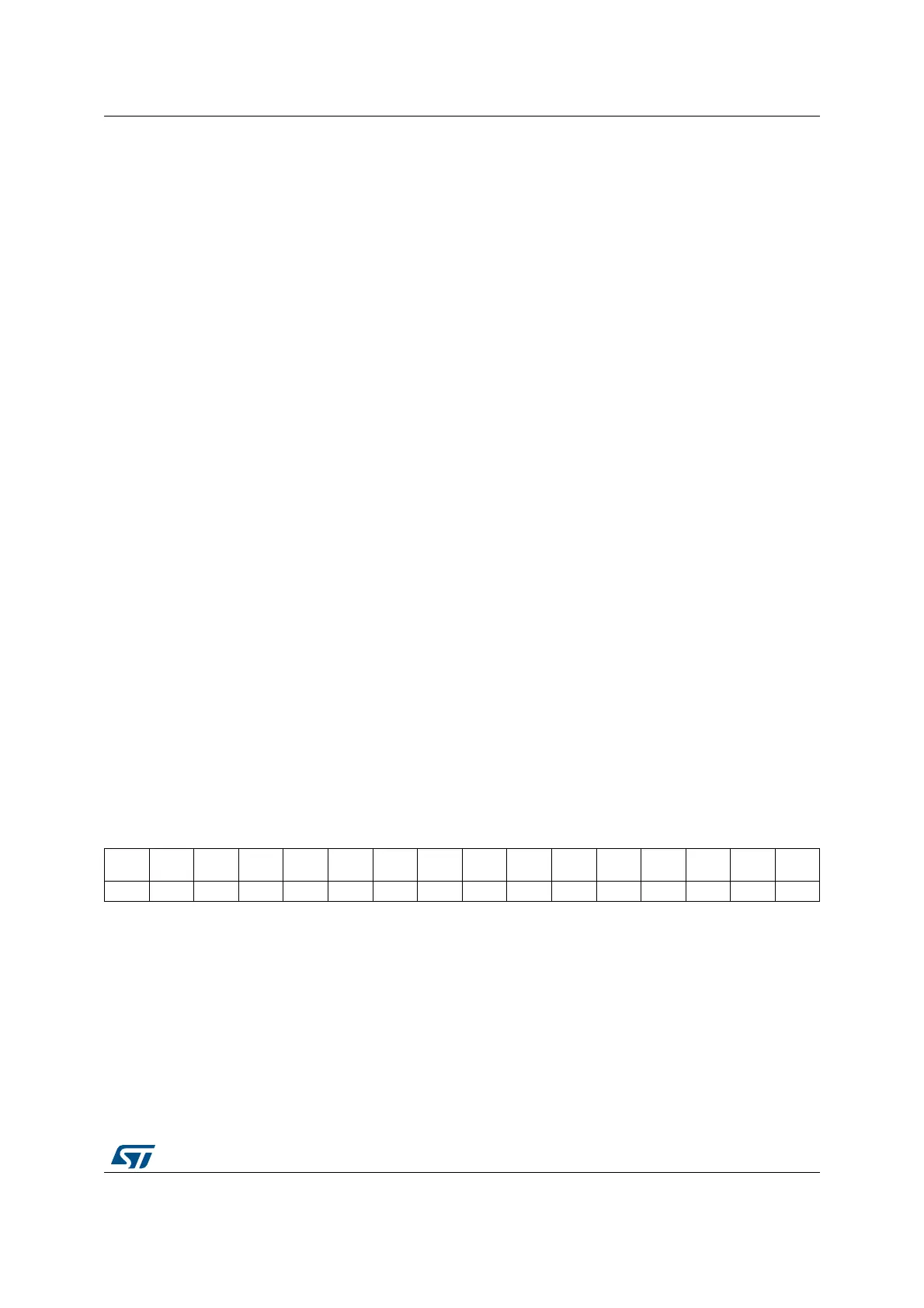

30.7.4 TIM15 DMA/interrupt enable register (TIM15_DIER)

Address offset: 0x0C

Reset value: 0x0000

Bits 16, 2, 1, 0 SMS[3:0]: Slave mode selection

When external signals are selected the active edge of the trigger signal (tim_trgi) is linked to

the polarity selected on the external input (see Input Control register and Control Register

description.

0000: Slave mode disabled - if CEN = ‘1’ then the prescaler is clocked directly by the

internal clock.

0001: Reserved

0010: Reserved

0011: Reserved

0100: Reset Mode - Rising edge of the selected trigger input (tim_trgi) reinitializes the

counter and generates an update of the registers.

0101: Gated Mode - The counter clock is enabled when the trigger input (tim_trgi) is high.

The counter stops (but is not reset) as soon as the trigger becomes low. Both start

and stop of the counter are controlled.

0110: Trigger Mode - The counter starts at a rising edge of the trigger tim_trgi (but it is not

reset). Only the start of the counter is controlled.

0111: External Clock Mode 1 - Rising edges of the selected trigger (tim_trgi) clock the

counter.

1000: Combined reset + trigger mode - Rising edge of the selected trigger input (tim_trgi)

reinitializes the counter, generates an update of the registers and starts the counter.

1001: Combined gated + reset mode - The counter clock is enabled when the trigger input

(tim_trgi) is high. The counter stops and is reset) as soon as the trigger becomes low.

Both start and stop of the counter are controlled.

Others: Reserved.

Note: The gated mode must not be used if tim_ti1f_ed is selected as the trigger input

(TS=’00100’). Indeed, tim_ti1f_ed outputs 1 pulse for each transition on tim_ti1f,

whereas the gated mode checks the level of the trigger signal.

Note: The clock of the slave peripherals (timer, ADC, ...) receiving the tim_trgo signal must be

enabled prior to receive events from the master timer, and the clock frequency

(prescaler) must not be changed on-the-fly while triggers are received from the master

timer.

1514131211109876543210

Res. TDE

COMD

E

Res. Res. CC2DE CC1DE UDE BIE TIE COMIE Res. Res. CC2IE CC1IE UIE

rw rw rw rw rw rw rw rw rw rw rw

Bit 15 Reserved, must be kept at reset value.

Bit 14 TDE: Trigger DMA request enable

0: Trigger DMA request disabled

1: Trigger DMA request enabled

Bit 13 COMDE: COM DMA request enable

0: COM DMA request disabled

1: COM DMA request enabled

Bits 12:11 Reserved, must be kept at reset value.

Loading...

Loading...