Basic timers (TIM6/TIM7) RM0440

1460/2126 RM0440 Rev 4

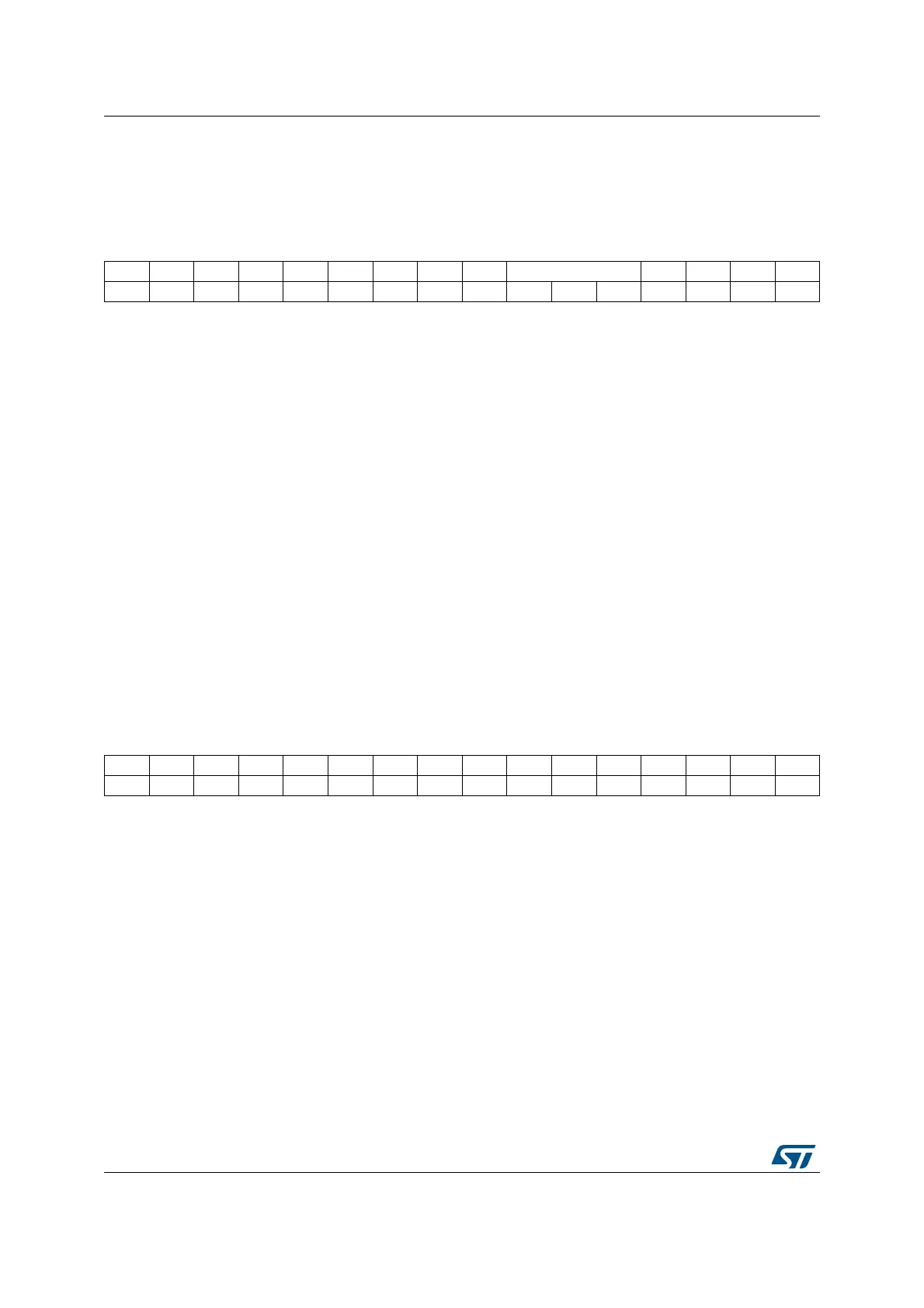

31.4.2 TIMx control register 2 (TIMx_CR2)(x = 6 to 7)

Address offset: 0x04

Reset value: 0x0000

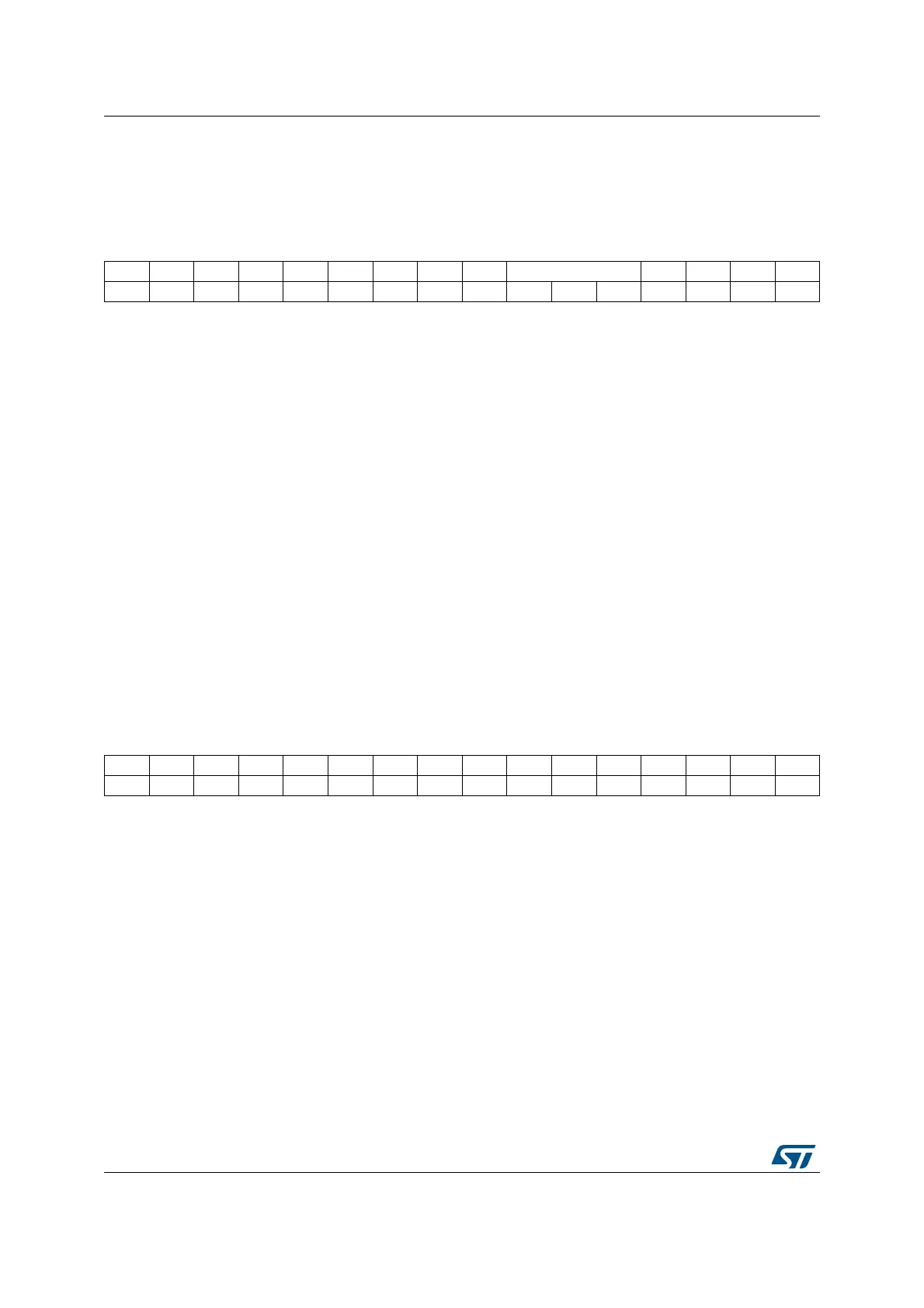

31.4.3 TIMx DMA/Interrupt enable register (TIMx_DIER)(x = 6 to 7)

Address offset: 0x0C

Reset value: 0x0000

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. MMS[2:0] Res. Res. Res. Res.

rw rw rw

Bits 15:7 Reserved, must be kept at reset value.

Bits 6:4 MMS[2:0]: Master mode selection

These bits are used to select the information to be sent in master mode to slave timers for

synchronization (TRGO). The combination is as follows:

000: Reset - the UG bit from the TIMx_EGR register is used as a trigger output (tim_trgo).

001: Enable - the Counter enable signal, tim_cnt_en, is used as a trigger output (tim_trgo).

It is useful to start several timers at the same time or to control a window in which a slave

timer is enabled. The Counter Enable signal is generated when the CEN control bit is

written.

010: Update - The update event is selected as a trigger output (tim_trgo). For instance a

master timer can then be used as a prescaler for a slave timer.

Note: The clock of the slave timer or he peripheral receiving the tim_trgo must be enabled

prior to receive events from the master timer, and must not be changed on-the-fly while

triggers are received from the master timer.

Bits 3:0 Reserved, must be kept at reset value.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. UDE Res. Res. Res. Res. Res. Res. Res. UIE

rw rw

Bits 15:9 Reserved, must be kept at reset value.

Bit 8 UDE: Update DMA request enable

0: Update DMA request disabled.

1: Update DMA request enabled.

Bits 7:1 Reserved, must be kept at reset value.

Bit 0 UIE: Update interrupt enable

0: Update interrupt disabled.

1: Update interrupt enabled.

Loading...

Loading...