Tamper and backup registers (TAMP) RM0440

1590/2126 RM0440 Rev 4

36.6.7 TAMP status clear register (TAMP_SCR)

Address offset: 0x3C

System reset value: 0x0000 0000

Bit 21 ITAMP6MF: ST manufacturer readout tamper interrupt masked flag

This flag is set by hardware when the internal tamper 6 interrupt is raised.

Bit 20 ITAMP5MF: RTC calendar overflow tamper interrupt masked flag

This flag is set by hardware when the internal tamper 5 interrupt is raised.

Bit 19 ITAMP4MF: HSE monitoring tamper interrupt masked flag

This flag is set by hardware when the internal tamper 4 interrupt is raised.

Bit 18 ITAMP3MF: LSE monitoring tamper interrupt masked flag

This flag is set by hardware when the internal tamper 3 interrupt is raised.

Bit 17 Reserved, must be kept at reset value.

Bit 16 Reserved, must be kept at reset value.

Bits 15:3 Reserved, must be kept at reset value.

Bit 2 TAMP3MF: TAMP3 interrupt masked flag

This flag is set by hardware when the tamper 3 interrupt is raised.

Bit 1 TAMP2MF: TAMP2 interrupt masked flag

This flag is set by hardware when the tamper 2 interrupt is raised.

Bit 0 TAMP1MF: TAMP1 interrupt masked flag

This flag is set by hardware when the tamper 1 interrupt is raised.

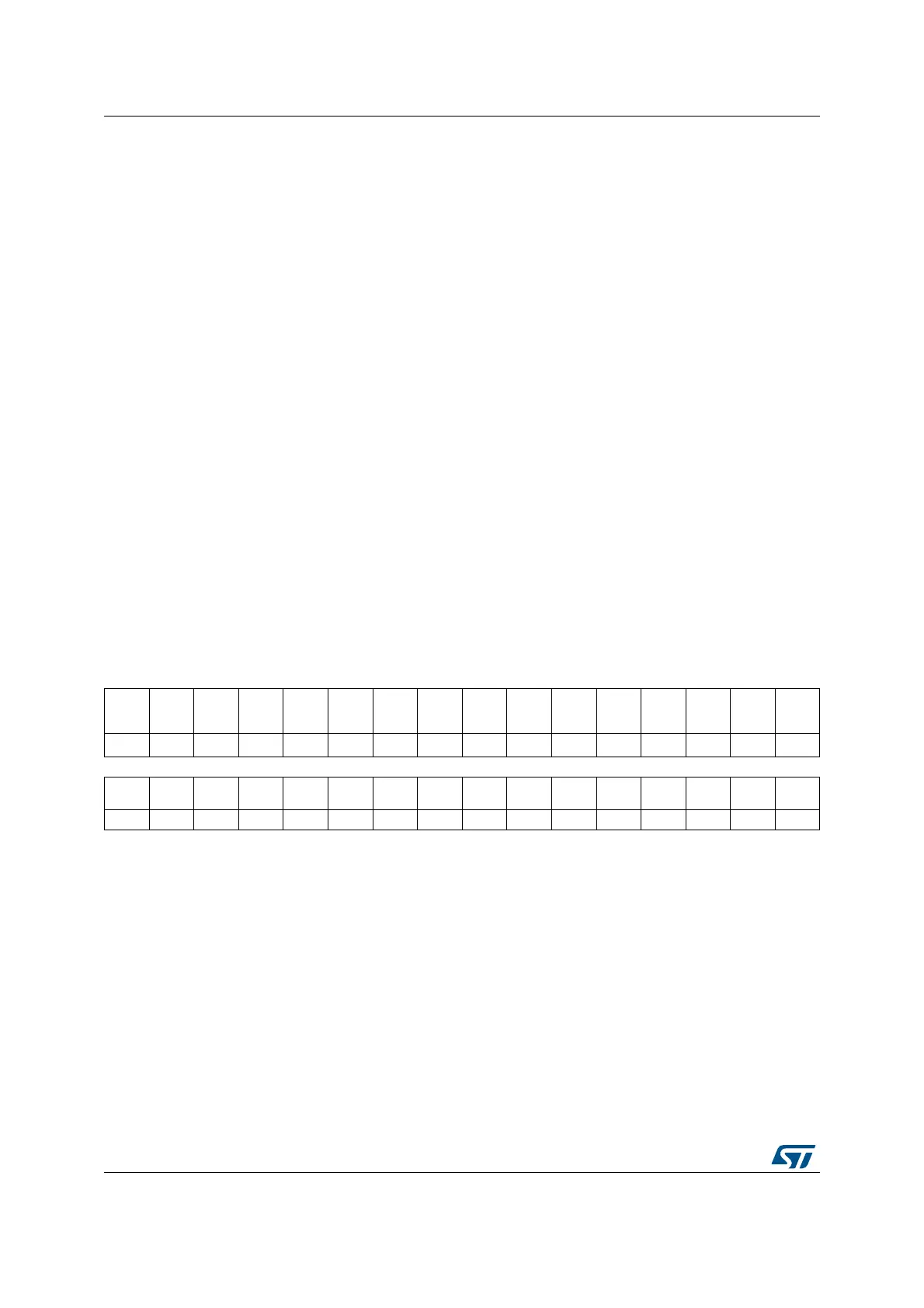

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

C

ITAMP

6F

C

ITAMP

5F

C

ITAMP

4F

C

ITAMP

3F

Res. Res.

w

w

ww

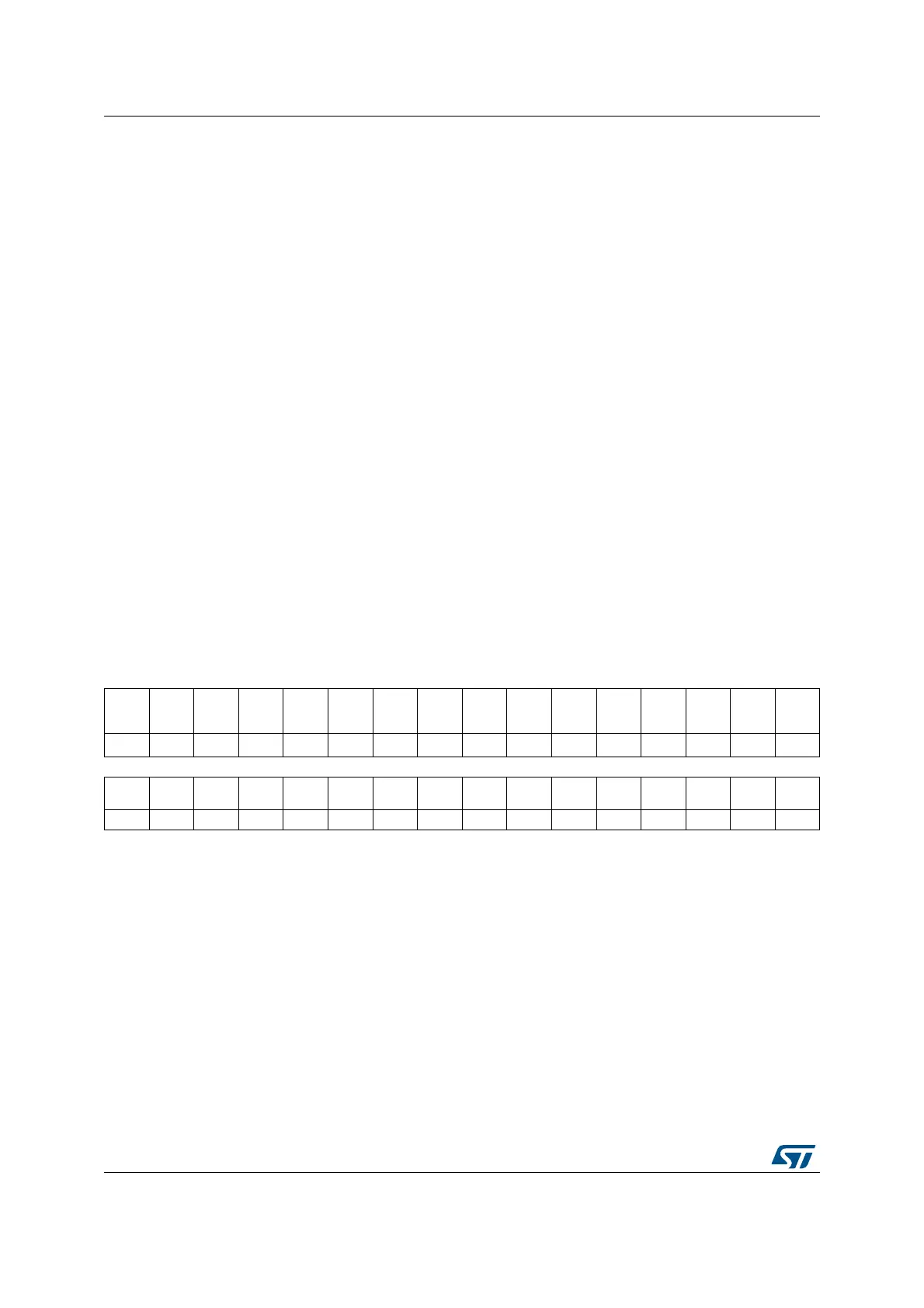

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

CTAMP

3F

CTAMP

2F

CTAMP

1F

www

Bits 31:24 Reserved, must be kept at reset value.

Bit 23 Reserved, must be kept at reset value.

Bit 22 Reserved, must be kept at reset value.

Bit 21 CITAMP6F: Clear ITAMP6 detection flag

Writing 1 in this bit clears the ITAMP6F bit in the TAMP_SR register.

Bit 20 CITAMP5F: Clear ITAMP5 detection flag

Writing 1 in this bit clears the ITAMP5F bit in the TAMP_SR register.

Bit 19 CITAMP4F: Clear ITAMP4 detection flag

Writing 1 in this bit clears the ITAMP4F bit in the TAMP_SR register.

Bit 18 CITAMP3F: Clear ITAMP3 detection flag

Writing 1 in this bit clears the ITAMP3F bit in the TAMP_SR register.

Loading...

Loading...