Filter math accelerator (FMAC) RM0440

512/2126 RM0440 Rev 4

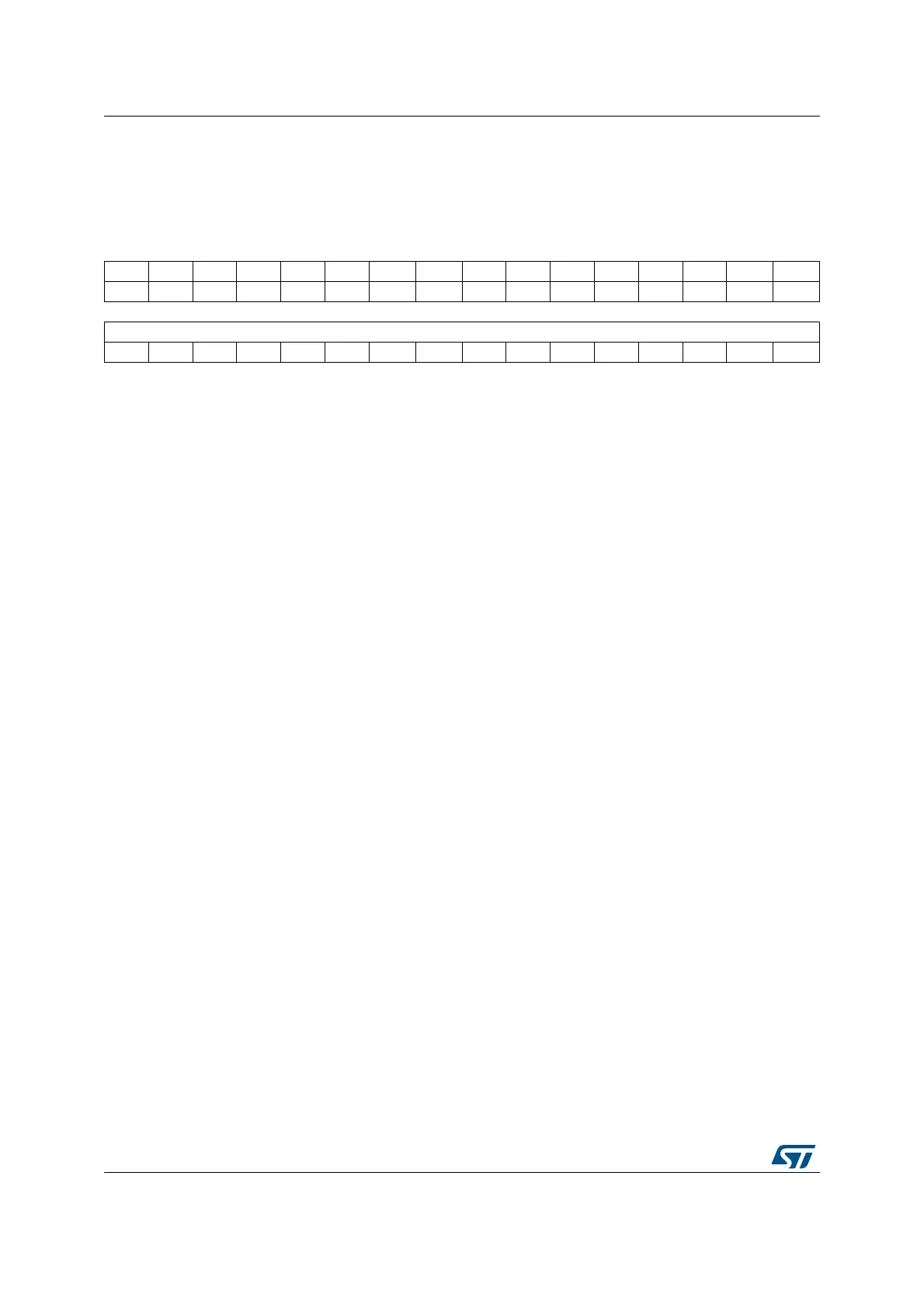

18.4.8 FMAC read data register (FMAC_RDATA)

Address offset: 0x1C

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109 8 765432 1 0

RDATA[15:0]

rrrrrr r r rrrrrr r r

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 RDATA[15:0]: Read data

When a read access to this register occurs, the read data are the contents of the Y output

buffer at the address offset indicated by the READ pointer. The pointer address is

automatically incremented after each read access.

Loading...

Loading...